主题中讨论的其他器件: ADS8881

我最近购买了此 ADC、并希望将其输出(转换结果)连接到 FPGA。

- 如何像使用非常简单的 ADC (数字输出中的模拟)、没有寄存器、没有编程等一样使用它?我应该直接从主器件输入 SDI 引脚无效命令吗?

- 我是否需要将每个引脚连接到某个引脚?

- 如果我的模拟输入是单端输入、我是否只需将负模拟输入与 GND 相连?

- 我是否可以使用任何电源配置来满足我在(1)中的需求? ?

- 我是否必须连接旁路电容器?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我最近购买了此 ADC、并希望将其输出(转换结果)连接到 FPGA。

您几乎肯定需要对 ADS127L11寄存器进行一些最低限度的编程。 复位时、输出数据速率和其他基本设置不太可能适合您的应用。 数据表中对串行接口进行了详细说明。 NOOP 命令在读取数据时很有用

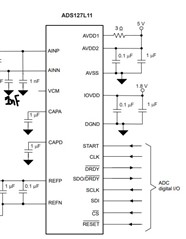

2、 大多数引脚都需要连接。 第9.2节显示了一个基本系统的良好示例。

3.可能。 取决于您的电源配置、但 GND 可能是一个候选器件。

4.您可以使用您希望 a)满足数据表要求的任何电源配置、B)支持对所需信号的测量。

5.如果你想要任何性能. 如果没有旁路电容器和精心设计的输入滤波器、您也可以使用更低的位数 ADC、因为您永远不会看到接近24个有用位的任何内容。

您好 Youssef、

ADS127L11有很多选择、并且需要一个外部时钟来获得数据表性能。 复位时、它默认为内部振荡器、必须更新内部寄存器以启用外部时钟源。 但是、如果您只希望器件正常工作、则可以将 SDI 接地、这将被解释为 NOP 命令、并且器件将使用输出数据速率约为400ksps 的内部振荡器运行。

如果 您需要简单、更高数据速率的器件、则 ADS8881是一款1MSPS 18b 器件、不需要配置、可能更适合。

ADS127L11的输出是一个二进制补码整数、它已经是定点。

ADS127L11仅支持 SPI 模式1。 在硬件级别、您可以采用3线或4线配置进行连接。

根据 Benjamin 的意见、您将需要使用旁路电容器;由于 IO 线路上产生的噪声、我怀疑您可以使 ADC 在没有这些电容器的情况下正常工作。 有关示例配置原理图、请参阅 ADS127L11EVM-PDK 用户指南。

此致、

Keith Nicholas

精密 ADC 应用

感谢您和 Benjamin 的回答

只要 START 引脚处于高电平、您就会读取数据、但器件寄存器将根据复位规格进行配置-这可能是或可能不是您的应用的理想选择。

2.只要这是一个合适的地方,我们就不能告诉你它是不是不是,因为我们不知道它的引用是什么。

它应该是符合数据表规格的任何电压。 0.5V -> 2.75V 用于低范围测量;1V ->(AVVD1 -AVSS)用于高范围测量。 您需要将某些器件连接到 REFN 和 REFP、因为它是一个差分输入。 如果您的基准源是单端的、则 REFN 可以连接到 AGND。

4.您需要在 AVDD、IOVDD、CAPA、CAPD 上至少设置电容、并在输入信号和基准电压上进行一些 RC 滤波。 为了甚至接近数据表中有关精度和噪声的规格、您需要仔细考虑所有这些因素。

您是否实际阅读过数据表? 您的问题并不完全隐藏在隐蔽的地方。

当我问这些问题时、我很仔细地问了一下、然后我开始实际阅读了这些问题。

您好,Youssef,

1、 内部寄存器包含您最后写入的值、因此在上电或复位后只需写入一次。 初始写入后、如果您想将器件配置更改为其他内容、当然可以再次写入这些寄存器。

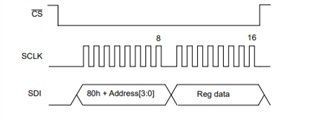

2. 要对内部寄存器进行写操作,需要发送一个16位字。 前4位是写入命令0x8h、后跟4b 地址、最后是要写入寄存器的8b 数据。 例如、为了选择外部时钟、您需要发送以下16b:

0x8880h、或0x1000 1000 1000 0000b

另一个示例是、如果要启用内部输入缓冲区、应将以下内容写入 CONFIG1寄存器:

0x8503h 或0x1000 0101 0000 0011b

此致、

Keith

好的、现在我已经将它与 FPGA 连接了。 即使模拟输入(要转换的信号)甚至没有被插入、它也会发送数据、而无需我通知它读取特定的寄存器。 您是否知道问题是什么?

(我只通过写入 CONFIG4寄存器来配置它,我想使用外部时钟(20MHz)。 在我按下按钮写入此命令后、它会发送此命令

FPGA)、除此之外什么都没有。 仅当我想读取 CONFIG4寄存器(通过按下另一个按钮)时、该波形才会改变。

我是否卡在读取特定寄存器的示例或什么? 我真的不知道为什么只有这个波形。

您好 Youssef、

除了器件仅在/CS 被拉至低电平时响应、ADS127L11通常在 START 引脚保持高电平时使用。 在此模式下、当新数据准备好进行检索时、它会通过拉低来持续转换数据并更新/DRDY 引脚。

在这种情况下、FPGA 需要监控/DRDY 引脚、当它转换为低电平时、您将把/CS 拉至低电平并时钟输出转换结果。 这假设 SDI 引脚保持低电平;如果之前的 SPI 帧发出了读取寄存器命令、则可以检索寄存器的内容。 数据表中的图8-27显示了这些详细信息。

希望这对您有所帮助。 周末愉快!

此致、

Keith

您好 Benjamin、

是的、我知道它不会自己发送数据、这就是为什么我想知道为什么每帧都有相同的输出、即使我没有将任何模拟信号连接到 ADC 的模拟输入。 我以为我一直在读取寄存器或类似的内容、但我没有、 因为在配置寄存器后、我向 SDI 引脚发送了 NOP、因此它应该在读取转换数据。

然后、我发现我错误地将 RESET 引脚(低电平有效)连接到 GND。 欢迎来到我的生活

如果您将器件配置为启动/停止模式、并且将 START 引脚设置为高电平、则每次有新的转换可用时 DRDY#都应脉冲为低电平。 很难断开该功能。

如果 DRDY#未变为低电平、那么我敢打赌以下事情之一

1) 1) RESET#引脚仍有问题。

2) 2)您没有将 START 设置为高电平(或者、如果您未使用 START 引脚进行控制、则未发出 START 命令)

3) 3)您已将 DRDY#绑定到阻止其变为低电平的器件。

发布原理图可能会有所帮助。

1) 1)只要您确定 FPGA 将其驱动为高电平、就没有理由这样做。

您为什么不告诉我们 ADC 上的每个引脚到底连接了什么? 这个部件非常简单、以至于您实际上不应该在从它获得转换时遇到问题。 获得高质量转换是一个完全不同的问题、但获取 DRDY#信号和数据却非常简单

如果您的 DRDY#未切换为低电平、则不会正确连接。

您是否能够读取和写入寄存器? 例如、读取寄存器0x0C 是否返回0x40?

是的、我能够读取和写入寄存器。 我配置了4个寄存器并读取寄存器 CONFIG4中的内容(正确)。

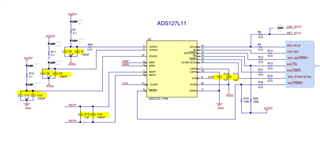

好的、我使用的是与此相同的、但/reset 连接到 IOVdd。

其余部分连接到 FPGA

是的、我在 CAPA 上有电容器、并且 CAPD 和 DGND 被连接。

是的、您说得对、我将其设置为0x80、但是。 这是我的答复中的一个排印错误。

我也尝试过、但仍然会出现相同的问题。 我将外部时钟设置为25.6MHz (根据数据表)、将 SCLK 设置为35MHz (数据表中写入的数据表中表明、对于2V 至5.5V 之间的 IOVDD、SCLK 的最小周期为20ns、最大1/4*(Fdata)(第6.8节)

您好 Youssef、

我的下一个建议是检查时钟。 一旦该器件配置为外部时钟、除非向 CLK 引脚施加适当的外部时钟信号、否则该器件不会进行转换。 该频率应介于0.5MHz 和26.2MHz 之间。 此时、/DRDY 引脚应在输出数据速率下具有或不具有 SPI 通信功能时发出低脉冲。 如果未连接、则其中一个引脚连接错误、或器件可能损坏。

您能否提供显示所有 ADS127L11引脚连接的原理图屏幕截图? 如果您使用的是 QFN 版本、则应将电源板接地。

此致、

Keith

您好 Youssef、

测量 IC 引脚处的时钟频率、确保其实际连接到时钟源。 由于您的 IOVDD=3.3V、因此时钟振幅也应为3.3V。

我建议使用 DMM 并测量每个引脚上的所有电压、以验证它们是否正确连接到3.3V、5V 或接地。

无任何通信、/CS=3.3V、启动=3.3V、/RESET=3.3V、SDI=0V、 您应该能够在输出数据速率下看到/DRDY 引脚脉冲。 假设您没有写入 CLK 选择位以外的任何其他寄存器位、则当 CLK=25.6MHz 时、/DRDY 的频率应为400kHz。

此致、

Keith

哇哦。 我真的很想在这里保持温柔、但这种设置令人非常怀疑。

这是一个具有重要信号完整性和电源要求的24位 ADC。

我看到大约20个地方、短路可能会破坏 ADC 的模拟部分。

实际上 不满足任何布局要求。

电容器不仅离器件太远、而且使用极长的引线进行连接、这真的很糟糕。

很抱歉、我是坏消息的传记者、但如果没有更好的设置、就会有人想知道为什么它不能为您服务。

此器件的 EVM 有一个原因(即使 TI 忘记了 R94,以后也必须添加它)

我真的建议购买价格非常合理的 EVM 模块之一、并将其连接到您的 FPGA 板。 如果 ADC 已正确通电并连接、则其工作原理会非常出色。 我现在正在完成一个基于它的设计、我对它的性能印象深刻。

您好,Youssef,

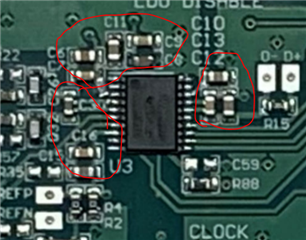

Ben 是正确的。 由于长引线的电感、您设置图片中的穿孔电容器将无法工作。 至少需要将表面贴装 SMT 电容器直接放置在适配器板上的 ADS127L11旁边。 下面重点介绍了所需的最小电容器。

如果您想使用此器件、最快的方法是使用评估板。 否则、您将需要将所有这些小部件直接焊接到 ADC 旁边、以使其正常工作。 为了获得接近数据表性能的任何东西、您需要一个完全定制的 PCB 设计。

此致、

Keith