主题中讨论的其他器件:DAC34H84、 DAC3484、 LMK04828、 CDCE62005

您好!

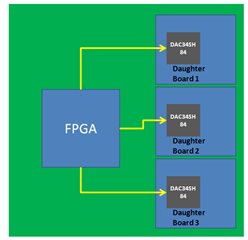

我们计划使用多个 FMC 板、每个板在具有 FPGA 的单个载板上具有一个 DAC34SH84。 系统的瞬时带宽为500MHz。 是否可与 DAC34SH84和 DAC34H84实现?

2)我们如何同步不同电路板上的器件(提到了用于同步的 OSTR)、但在物理上我们如何将它们连接到不同的 FMC 电路板。

3) DACCLK 和 OSTR 是差分信号、我们是否将多条(4条同轴/SMA 电缆)连接到每个电路板?

4) 4)我们是否可以将时钟生成芯片放在载板上、然后通过 FMC 连接器将其路由到 DAC IC?

5) 5)是否有将 FPGA (Xilinx)连接到这些 DAC 的参考设计?

6) 6)如果 I 和 Q 为具有单端输入的 IQ 调制器供电、DAC 必须生成零。 请提供有关合适电路的建议? 还必须执行 IQ 不平衡校正和 LO 泄漏校正。 由于 IC 已经具有此特性、如果使用运算放大器(如果输出为零、则会排除变压器)将差分信号转换为单端信号、我们将如何利用这些特性。 我们是否在运算放大器输出端添加某种偏置 t 以引入直流以消除 LO 泄漏?

感谢您的帮助、