Other Parts Discussed in Thread: DAC43401-Q1

大家好、

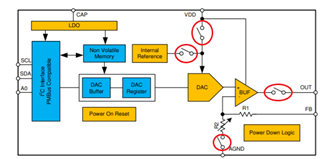

在下图中、我可以看到 VDD、REF、OUT 和 AGND 上有4个内部开关。

我的客户对内部开关有两个问题。

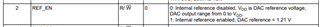

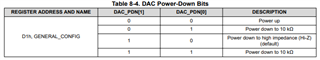

1.能否通过设置 EEPROM 来设置这些开关的初始开/关状态? 初始状态表示 POR 之后的状态。 我知道连接到 VDD 的开关的初始状态、REF 可以通过 D1h 的 REF_EN 位进行设置。 但是、OUT 和 AGND 上的开关如何?

2.您能告诉我 POR 后开关状态被设置的时序吗?

此致、

Saito

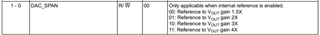

可变电阻器 R2决定基准增益设置。 这由 General_CONFIG 寄存器中的 DAC_SPAN 位进行设置。

可变电阻器 R2决定基准增益设置。 这由 General_CONFIG 寄存器中的 DAC_SPAN 位进行设置。  所有这些都可以保存在 EEPROM 中

所有这些都可以保存在 EEPROM 中