您好!

我刚刚开始使用 ADS7038。 我目前正在尝试使用手动模式读取全部8个输入、但芯片看起来只是从模拟0发送相同的值、而不会提前读取任何其他模拟点。

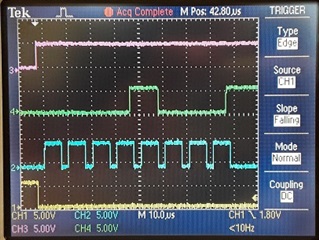

我将通过 SPI 端口与 ADS7038进行通信、我确信该接口能够正常工作、因为我可以向寄存器写入数据并成功读回该寄存器。

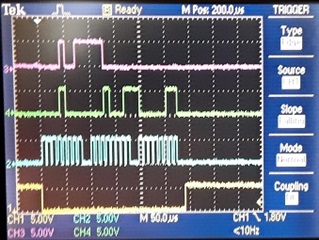

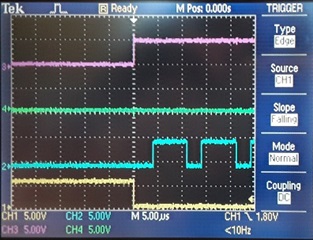

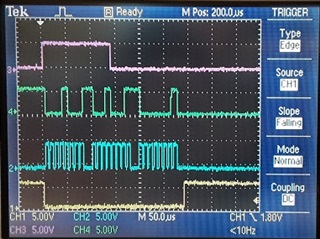

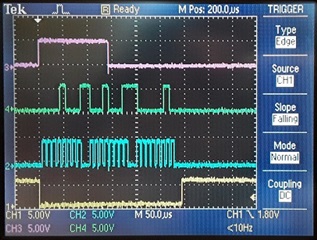

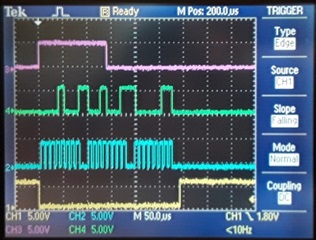

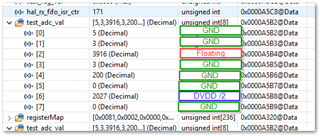

对于手动模式测试、看起来 ADS7038数据表第23页的所有初始设置(CONV_MODE=00、SEQ_MODE=00、PIN_CFG=0)都是它们的默认值、因此我没有更改任何初始值。 然后、我给 ADS7038提供了这3条命令、以查看是否可以读取前3个模拟输入(写入 CHANNEL SEL 寄存器、地址= 0x11):

08、11、01;将 MANUAL_Chid 设置为1以进行下一次读取

08、11、02;将 MANUAL_Chid 设置为2以进行下一次读取

08、11、03;将 MANUAL_Chid 设置为3以进行下一次读取

在每种情况下、当我查看接收到的数据时、它看起来就像我在上面提到的那样一直读取模拟0。

有人能不能告诉我、我做了些什么、我可以做些什么来解决这个问题?

感谢您的回答。

Brad McMillan