尊敬的团队

客户对 OSR 设置有两个问题、希望提出。 因为客户认为输出波形有疑问。

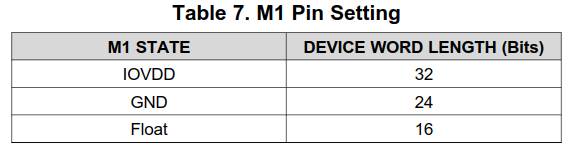

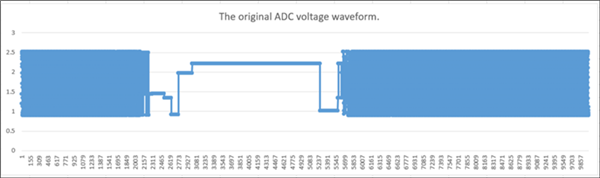

输入波形:

输入:0.5 Vpp,50Hz,正弦

问题1:

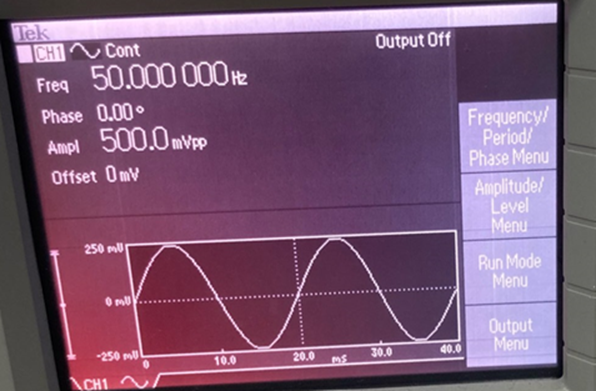

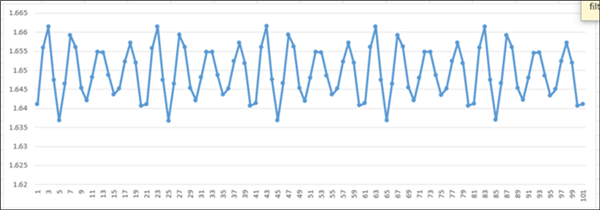

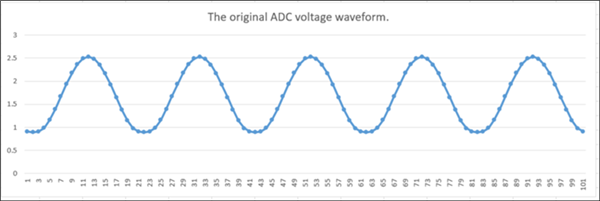

将 OSR 设置为4096、但观察由数字滤波器滤波的波形时会有很多噪声。 要观察 ADC 捕获的电压、您会发现电压波形不是正弦波。

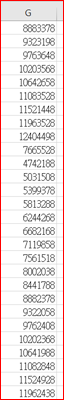

ADC CLK 设置:

ADC CLKIN = 16.384MHz

CLK_DIV = 001:fICLK = fCLKIN / 2

ICLK_DIV=001:FMOD = fICLK/2

OSR:0000:Fdata = Fmod / 4096

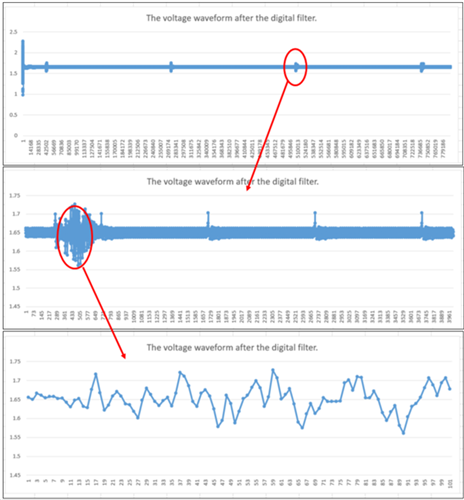

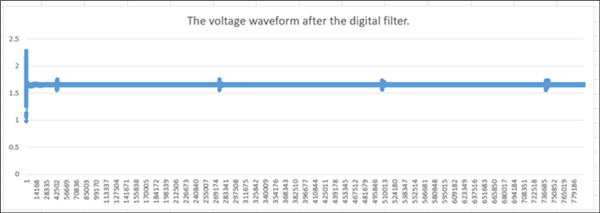

过滤器后的波形:

ADC 输出的正弦波波形:

相应 ADC 输出波形的缩放如下:

我是否可以问为什么会产生这种结果? 只要滤波器部件是水平线、ADC 输出波形就会非常漂亮。

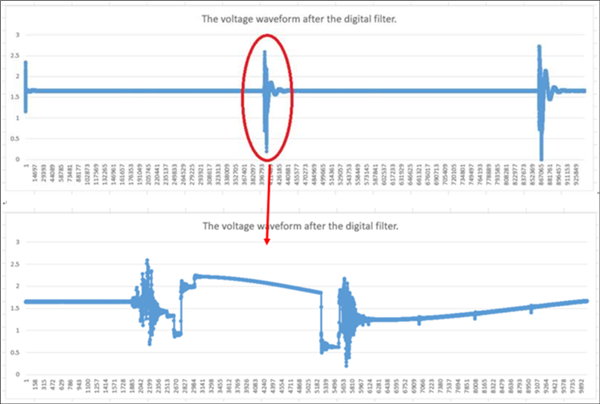

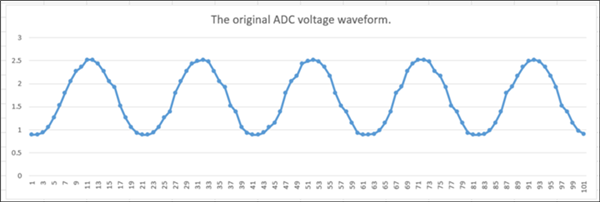

问题2:

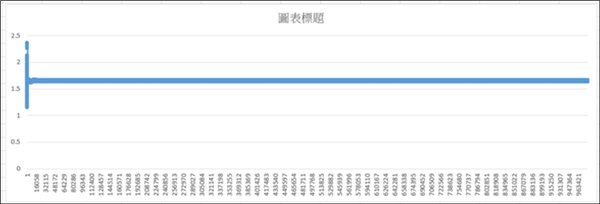

客户 将 OSR 设置为小于2048、输出将具有一个凸波。 (客户反馈)

ADC CLK 设置:

ADC CLKIN = 16.384MHz

CLK_DIV = 001:fICLK = fCLKIN / 2

ICLK_DIV=001:FMOD = fICLK/2

OSR:0001:Fdata = Fmod / 2048

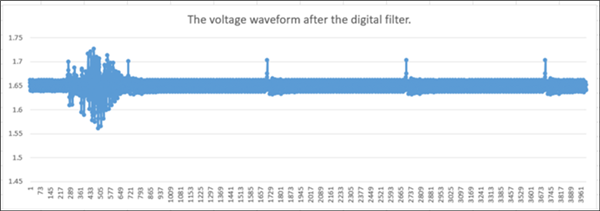

波形在滤波之后出现、波 形放大:

按如下方式放大相应 ADC 输出的正弦波波形:

滤波后的正常波形和放大波形:

按如下方式放大相应 ADC 输出的正弦波波形:

具有不同设置的滤波波波波波形如下所示:

ADC CLK 设置:

ADC CLKIN = 16.384MHz

CLK_DIV = 001:fICLK = fCLKIN / 2

ICLK_DIV=001:FMOD = fICLK/2

OSR:0001:Fdata = Fmod / 2048

ADC CLK 设置:

ADC CLKIN = 16.384MHz

CLK_DIV = 001:fICLK = fCLKIN / 2

ICLK_DIV=001:FMOD = fICLK/2

OSR:0010:Fdata = Fmod / 1024

ADC CLK 设置:

ADC CLKIN = 16.384MHz

CLK_DIV = 001:fICLK = fCLKIN / 2

ICLK_DIV=001:FMOD = fICLK/2

OSR:0101:Fdata = Fmod / 512

ADC CLK 设置:

ADC CLKIN = 16.384MHz

CLK_DIV = 001:fICLK = fCLKIN / 2

ICLK_DIV=001:FMOD = fICLK/2

OSR:1101:Fdata = Fmod / 64

如果您可以解释 ADC 中出现这些情况的原因吗?

非常感谢

丹尼