主题中讨论的其他器件:LMK04828、 LMX2594

大家好、

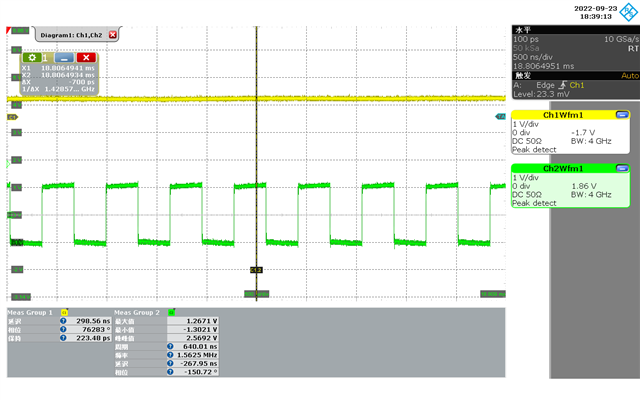

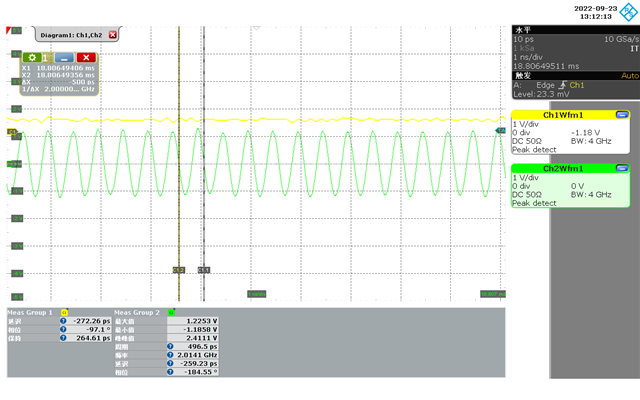

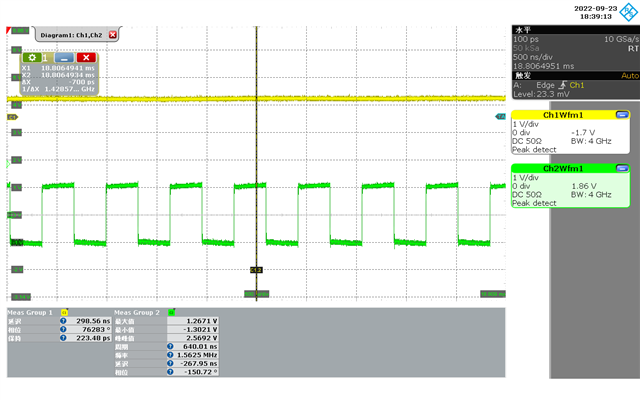

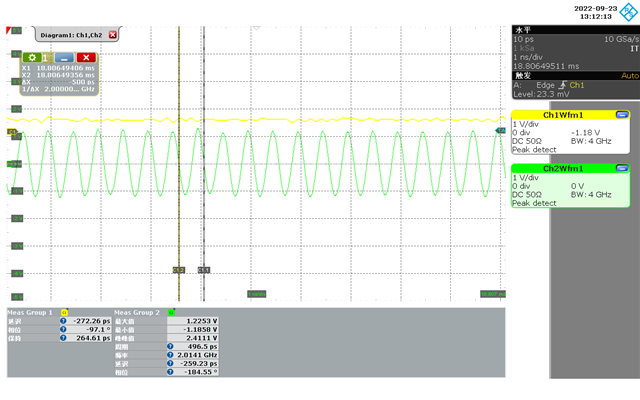

客户使用自己的设计板、FPGA 为420T、REFCLK 和 FPGA 的参考时钟由 LMK04828生成、LMK 连接 LMX2594以输出 ADC 器件时钟和参考时钟。 示波器可以观察生成的时钟信号。

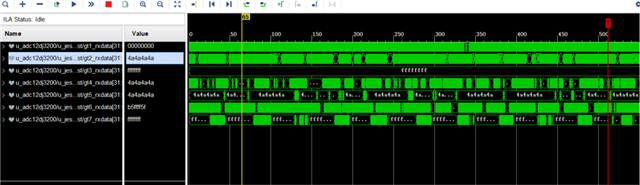

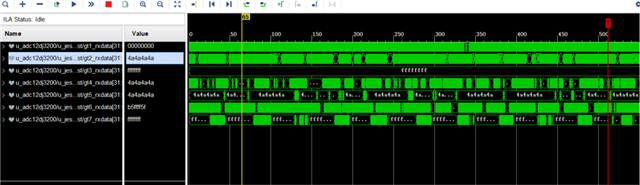

JMODE1、ILA 观察到的同步信号被拉低、但 xillnx IP 内核 tdata 没有数据输入(K28.5)、 并且无法完成 ADC 上的前台校准、0x6A 始终读取0C。

这是 ILA 捕获的信号

此致

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

客户使用自己的设计板、FPGA 为420T、REFCLK 和 FPGA 的参考时钟由 LMK04828生成、LMK 连接 LMX2594以输出 ADC 器件时钟和参考时钟。 示波器可以观察生成的时钟信号。

JMODE1、ILA 观察到的同步信号被拉低、但 xillnx IP 内核 tdata 没有数据输入(K28.5)、 并且无法完成 ADC 上的前台校准、0x6A 始终读取0C。

这是 ILA 捕获的信号

此致

这是寄存器配置:

分配 cfg_mem[0]={15'h0000, 8'hB0};//重置

分配 cfg_mem[1]={15'h0030、8'hFF};

分配 cfg_mem[2]={15'h0031、8'hFF};

分配 cfg_mem[3]={15'h0032、8'hFF};

分配 cfg_mem[4]={15'h0033、8'hFF};

预加釿 cfg_mem[5]={15'h00488'h03};//将串行器预加重设置为3 μ s

分配 cfg_mem[6]={15'h0200、8'00};//对 JESD_EN=0进行编程以停止 JESD204B 状态机并允许更改设置。

分配 cfg_mem[7]={15'h0061、8'00};//编程 CAL_EN=0以停止校准状态机并允许更改设置

分配 cfg_mem[8]={15'h0201、8'h01};//对所需的 JMODE 进行编程。 JMODE=1

分配 cfg_mem[9]={15'h0202,8'h1f};//编程所需的 KM1值。 Km1 = K-1

根据需要分配 cfg_mem[10]={15'h0204,8'h06};//对 SYNC_SEL 进行编程。

分配 cfg_mem[11]={15'h003B、8'h03};//TMSTP 输入使能和 LVPECL

分配 cfg_mem[12]={15'h0205,8'h04};//测试模式0x00刿0xFF 测试链路屿斜坡测试模式

超量稿 cfg_mem[13]={15'h0213、8'h07};//启用超范围、将超范围保持设置为最大周期8*2^7 = 1024个样本8*2^7 = 1024 μ s

分配 cfg_mem[14]={15'h0029、8'h70};

分配 cfg_mem[15]={15'h0029、8'h73};

分配 cfg_mem[16]={15'h0061、8'h01};//编程 CAL_EN=1以启用校准状态机。

分配 cfg_mem[17]={15'h0200、8'h01};//对 JESD_EN=1进行编程以重新启动 JESD204B 状态机并允许链接重新启动

将 cfg_mem[14]={15'h006C、8'00};//将 CAL_SOFT_TRIG 设置为低电平以重置校准状态机

将 cfg_mem[15]={15'h006C、8'h01};//将 CAL_SOFT_TRIG 设置为高电平以启用校准

分配 cfg_mem[18]={15'h02C0、8'00};

分配 cfg_mem[19]={15'h02C2,8'00};

分配 cfg_mem[20]={15'h02C1、8'h1f};

您可以提出任何故障排除建议吗?

尊敬的 Rui:

首先、让我们确保 FG CAL 运行正常。 通常、当 FG 校准失败时、这意味着器件未接收 CLK。 加电后和复位前、请确保应用器件 CLK。 您能否在 CLK 的输入引脚上进行测量以进行确认?

复位后、请等待寄存器0x270 的位0为高电平。 当初始化逻辑完成 时(~250ms)、该位返回1、但出于调试目的、我建议 等待1秒、并在您有一个具有时间基准的工作系统后进行优化。

分配 cfg_mem[0]={15'h0000, 8'hB0};//重置

等待 INIT 位在复位后完成。 寄存器0x270位0

分配 cfg_mem[6]={15'h0200、8'00};//对 JESD_EN=0进行编程以停止 JESD204B 状态机并允许更改设置。

分配 cfg_mem[7]={15'h0061、8'00};//编程 CAL_EN=0以停止校准状态机并允许更改设置

分配 cfg_mem[1]={15'h0030、8'hFF};

分配 cfg_mem[2]={15'h0031、8'hFF};

分配 cfg_mem[3]={15'h0032、8'hFF};

分配 cfg_mem[4]={15'h0033、8'hFF};

预加釿 cfg_mem[5]={15'h00488'h03};//将串行器预加重设置为3 μ s

分配 cfg_mem[8]={15'h0201、8'h01};//对所需的 JMODE 进行编程。 JMODE=1

分配 cfg_mem[9]={15'h0202,8'h1f};//编程所需的 KM1值。 Km1 = K-1

根据需要分配 cfg_mem[10]={15'h0204,8'h06};//对 SYNC_SEL 进行编程。

分配 cfg_mem[11]={15'h003B、8'h03};//TMSTP 输入使能和 LVPECL

分配 cfg_mem[12]={15'h0205,8'h04};//测试模式0x00刿0xFF 测试链路屿斜坡测试模式

超量稿 cfg_mem[13]={15'h0213、8'h07};//启用超范围、将超范围保持设置为最大周期8*2^7 = 1024个样本8*2^7 = 1024 μ s

分配 cfg_mem[14]={15'h0029、8'h70};

分配 cfg_mem[15]={15'h0029、8'h73};

分配 cfg_mem[16]={15'h0061、8'h01};//编程 CAL_EN=1以启用校准状态机。

分配 cfg_mem[17]={15'h0200、8'h01};//对 JESD_EN=1进行编程以重新启动 JESD204B 状态机并允许链接重新启动

将 cfg_mem[14]={15'h006C、8'00};//将 CAL_SOFT_TRIG 设置为低电平以重置校准状态机

将 cfg_mem[15]={15'h006C、8'h01};//将 CAL_SOFT_TRIG 设置为高电平以启用校准

分配 cfg_mem[18]={15'h02C0、8'00};

分配 cfg_mem[19]={15'h02C2,8'00};

分配 cfg_mem[20]={15'h02C1、8'h1f};

从 cal_status 拉至 FG_DONE

在我结束时、当我关闭时钟或将时钟减少到特定点时、只有 INIT 位在复位后不会清除、并且如果没有时钟 FG 校准将不会完成。 您是否正在使用我提供的新产品?

对于您为时钟提供的图片、只有1个桥臂(仅限+ CH)还是差分? VCM 处于低侧... 您能否测量最靠近引脚的电源电压(尝试使用去耦电容器)以确保它们在数据表中并且源极具有为 ADC 供电的适当额定电流。 您能否检查要计时的交流电容器。 您能否共享设计原理图?

上电后、clk 处于活动状态且 复位已置为有效。 尝试以下寄存器写入...

0x0200 0x00 //清除 JESD_EN (始终在 CAL_EN 之前)

0x0061 0x00 //清除 CAL_EN (始终位于 JESD_EN 之后)

0x0201 0x00 //设置 JMODE0

0x0202 0x03 //设置 KM1=3、因此 K=4

0x0204 0x01 //使用 SYNCSE 输入、偏移二进制数据、启用扰频器

0x0213 0x07 //启用超范围,将超范围保持设置为最大周期8*2^7=1024个样本

0x0048 0x03 //将串行器预加重设置为3

0x0061 0x01 //设置 CAL_EN (始终在 JESD_EN 之前)

0x0200 0x01 //设置 JESD_EN (始终在 CAL_EN 之后)

0x006C 0x00 //将 CAL_SOFT_TRIG 设置为低电平以复位校准状态机

0x006C 0x01 //将 CAL_SOFT_TRIG 设置为高电平以启用校准

读取寄存器0x208 (JESD_STATUS)并检查 PLL_LOCKED 是否为高电平(位2)。

您是否尝试了我一周前给您的序列、并测量了电源电压以关闭器件?

我要重新连接它。

上电后、clk 处于活动状态且 复位已置为有效。 尝试以下寄存器写入...

0x0200 0x00 //清除 JESD_EN (始终在 CAL_EN 之前)

0x0061 0x00 //清除 CAL_EN (始终位于 JESD_EN 之后)

0x0201 0x00 //设置 JMODE0

0x0202 0x03 //设置 KM1=3、因此 K=4

0x0204 0x01 //使用 SYNCSE 输入、偏移二进制数据、启用扰频器

0x0213 0x07 //启用超范围,将超范围保持设置为最大周期8*2^7=1024个样本

0x0048 0x03 //将串行器预加重设置为3

0x0061 0x01 //设置 CAL_EN (始终在 JESD_EN 之前)

0x0200 0x01 //设置 JESD_EN (始终在 CAL_EN 之后)

0x006C 0x00 //将 CAL_SOFT_TRIG 设置为低电平以复位校准状态机

0x006C 0x01 //将 CAL_SOFT_TRIG 设置为高电平以启用校准

读取寄存器0x208 (JESD_STATUS)并检查 PLL_LOCKED 是否为高电平(位2)。