大家好、

简而言之、我能够写入配置寄存器并读回它们。 但是、当进入 RDATAC 模式时、ADC 在采样时不会报告正确的数据。 每个通道都会卡在一个值上、并在每个 DRDY 下降沿周期上始终重复该值。

此时、我不确定是否在模拟侧设置了错误的 PDK 开发套件。 或者如果存在配置设置问题、ADC 将挂起。

我使用的是 ADS131E08-EBM-PDK 套件。 我移除了顶部板、并将 SPI 信号、DRDY 和复位输入连接到 FPGA 开发套件。

ADS131E08开发套件具有为电路板供电的5V 电压以及为 DVDD 电源轨提供的3.3V 电压。 通过跳线选择3V 单极模拟电源。 外部振荡器被启用、2.5V 被连接至 VREFP 以用作一个外部基准。 我在通道1上连接了+1.25V 电压、其余输入保持悬空。

FPGA 使用80ns SCLK、并遵循数据表中要求的 TCLK 延迟。 我将所有内容拆分为8个时钟周期、并在每个字节后插入 TCLK 延迟。 SCLK 只在写入/读取周期内运行。

启用 ADC 的过程是:

- 为 ADC 加电。 (ADC 复位保持高电平、START 保持高电平)

- 等待 VCAP 稳定

- 发出复位脉冲并等待18个 TCLKS

- 发送 SDATAC 命令

- 读取 CONFIG2、按预期接收0xE0

- 将0x40写入 CONFIG3 (使用外部基准)

- 将0xE4写入 CONFIG2 (禁用测试信号)

- 将0xD6写入 CONFIG1 (将速率设置为1K)

- 读取 CONFIG3= 0x41 (数据表显示 LSB 位是保留的、可以返回为1或0)

- 读取 CONFIG2= 0xE5

- 读取 CONFIG1 = 0xD6

- 将 START 信号设置为高电平(立即保持高电平)

- 等待4个 TCLK 周期(我是否需要在这里等待更长的时间、还是因为 DRDY 在就绪前不会变为低电平?)

- 发送 RDATAC 命令

- 等待直至 DRDY 变为低电平

- 每次 DRDY 变低时对 ADC 采样。 (每次在每个序列上、我都确认了正确的216个时钟周期)

- 对于 STATUS->I 得到0xC0F000 (正确的 ID,表示输入1-4出现故障,此时电压处于范围之内或根本没有施加电压?)

- 通道1回读0x640000

- 通道3-4始终读回0x800000

- 更改这些通道上的输入电压不会产生影响。 它始终报告相同的内容

我的另一个观察结果是、当我读取 ADC 时、会在下一个 SPI 周期输出下一个寄存器数据、此时要求仅读取一个通道。 它不会影响我,但这似乎是 ADC 的错误行为。

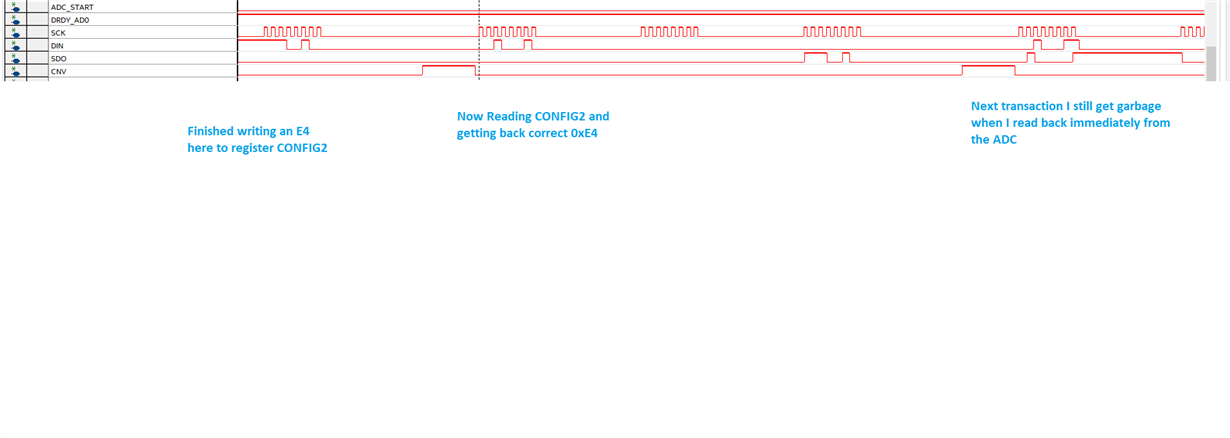

我已包括一些已标记的屏幕截图、其中显示了成功的配置读取、下一个 CS 周期中的奇怪下一个寄存器数据以及 ADC 采样。