主题中讨论的其他器件: DAC80004

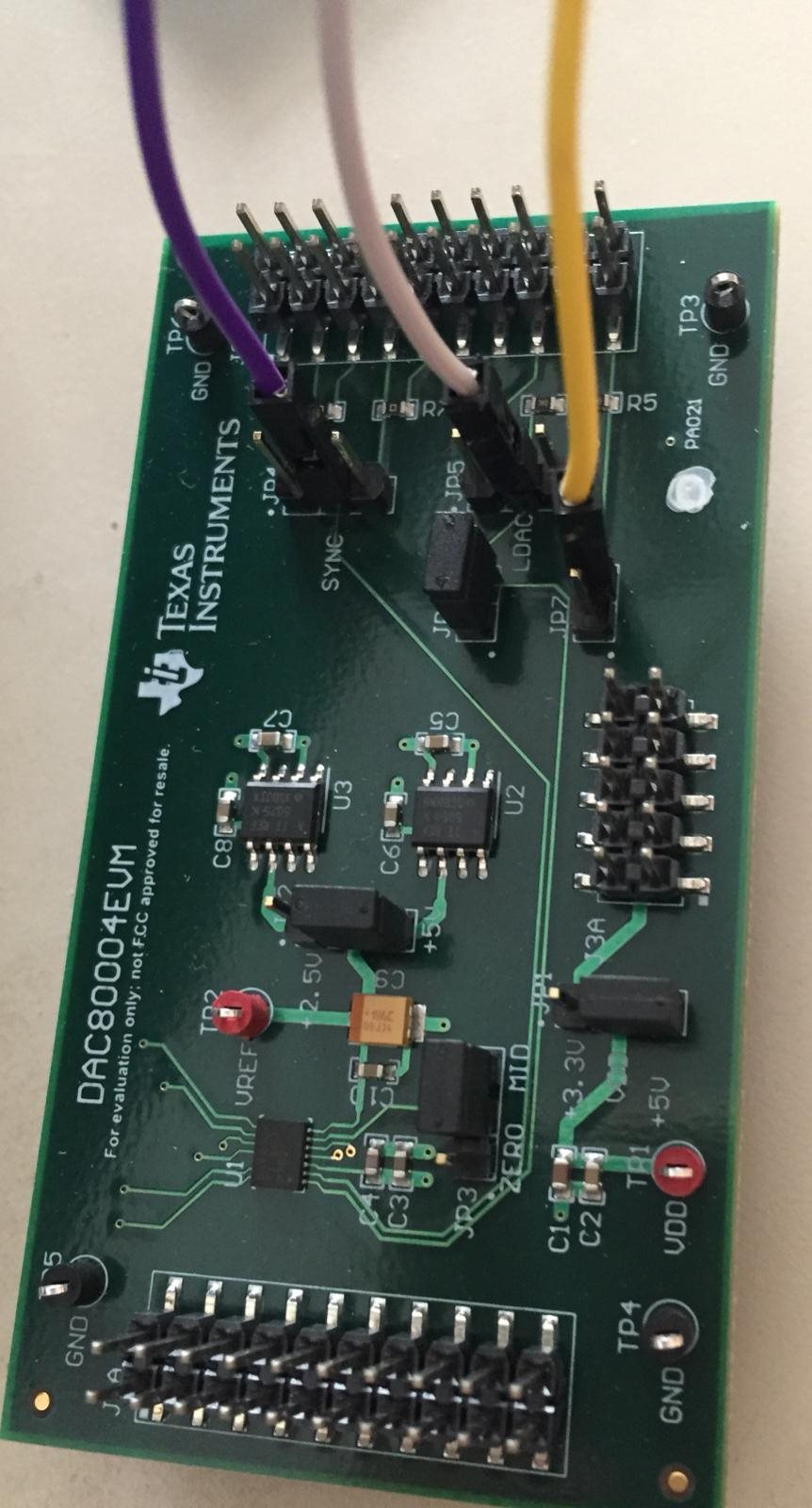

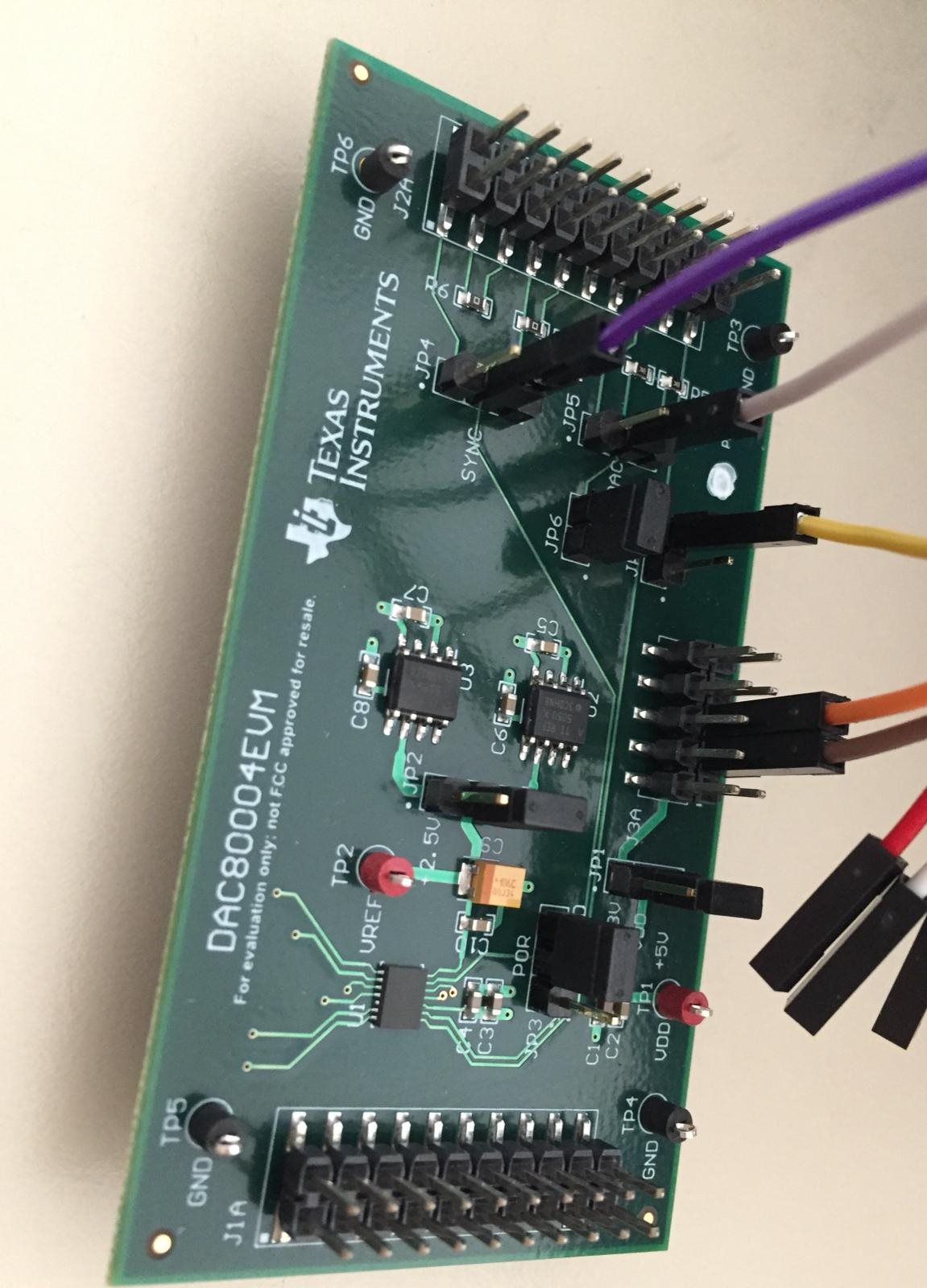

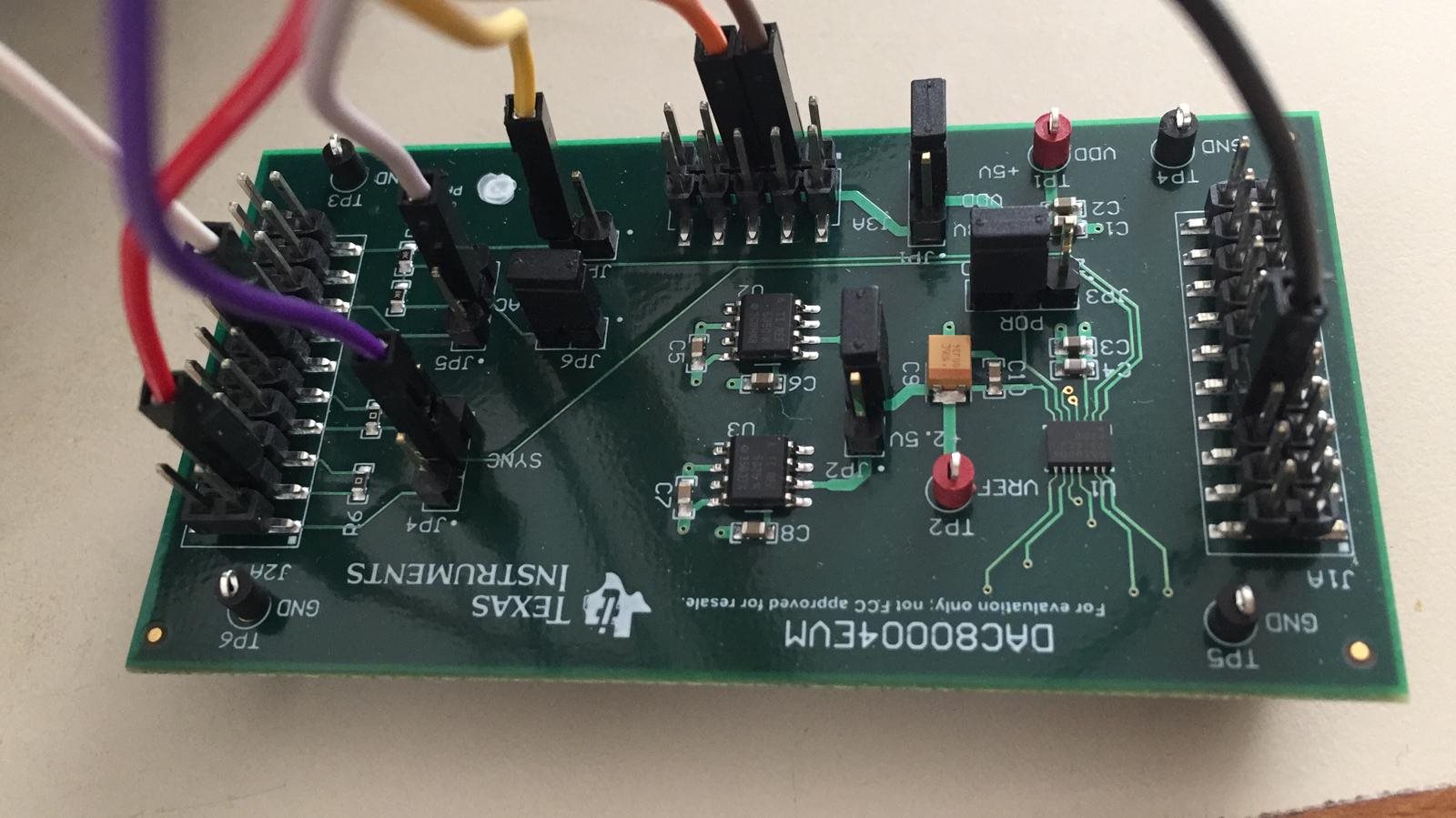

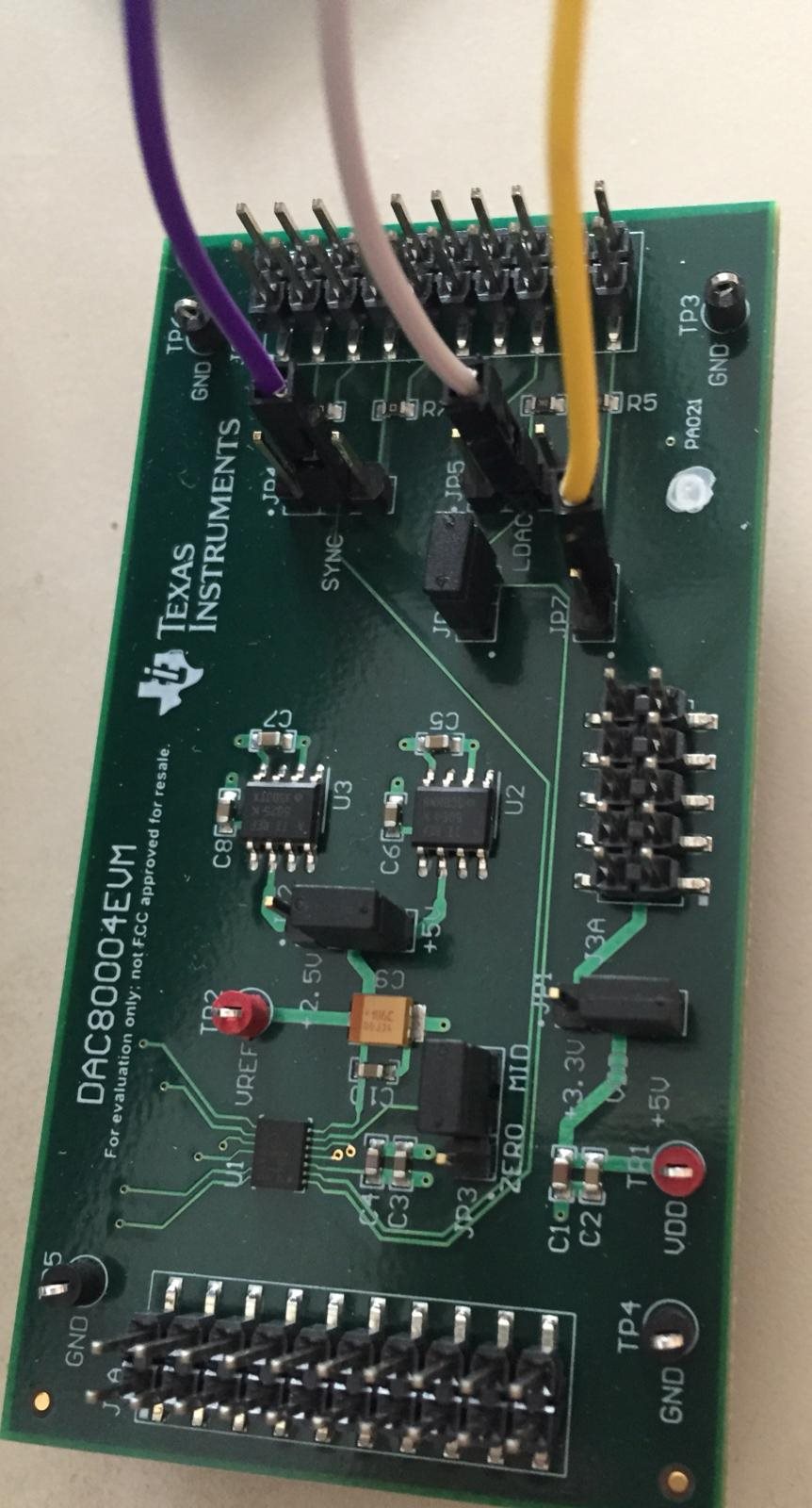

大家好、我已经购买了下面显示的 DAC80004EVM。

我想 使用 Jlink 调试器对其进行编程、左侧 POTO 下方显示了引脚排列。

DAC80004电路板上的 Jlink 引脚在哪里连接?

另外、关于 Vtref 引脚、我需要向电路板添加一个电压源、并将 Vtref 连接到电路板?

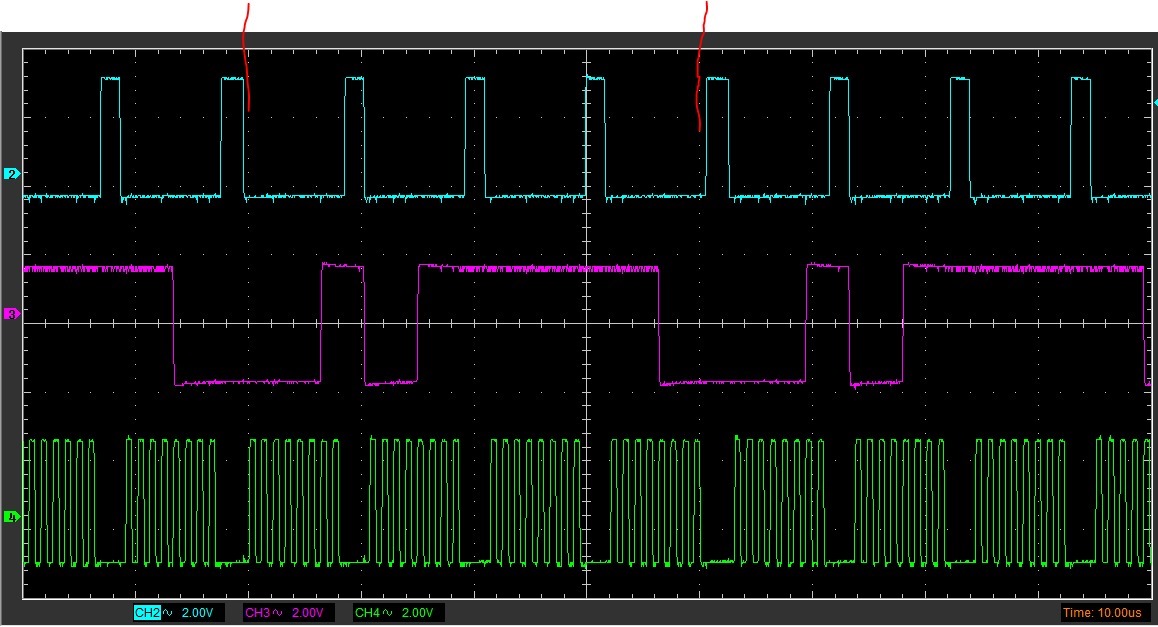

我之前已经对 DAC80004进行了编程,芯片在板上,我使用 JLINK SWD 连接连接到板上,并且我使用 SPI 命令与器件进行了通信。

我想使用我的 JLINK EDU 连接到 DAC80004EVM、并使用 SPI 与其通信

谢谢。