Other Parts Discussed in Thread: DAC5674

你(们)好,先生

我们使用的 IP 将生成正弦波样本、这些样本采用有符号格式。

我们是否可以将有符号值馈送到 DAC5674、DAC 是否会正确获取这些值并转换为模拟波形。

请对此进行澄清以解决我们的问题。

谢谢

Roja V

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

我们在外部时钟模式下使用 DAC5674。 x4为1、PLL VDD 为0v、HP1和 HP2为0。

外部源为 DAC 提供400MHz 时钟。

该时钟信号将传输到 DAC 和 FPGA。

我们使用 DDS IP 来生成样本、DDS 的输入时钟与 DAC 相同、即外部源为400MHz。

DDS 的输出为30MHz、因此我们可以获得13个样本以从样本重构正弦信号。

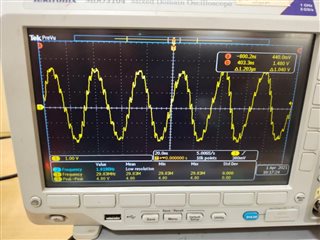

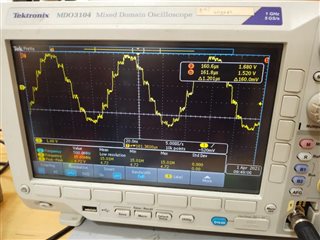

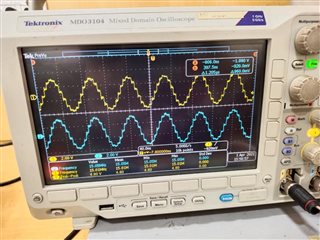

但 DAC 的输出提供正弦波。

我们观察到、正弦波被分配给频谱分析仪

功率级别 为-8dbm

SFDR 为64 DBC。

杂散在67MHz 下、 电平为-53dBm。

由于这种杂散、我们的 SFDR 正在下降、如何消除这种杂散。

请建议我们解决此问题。

请查找 DAC 的输出附件。

谢谢

Roja V

您好、Roja、

您使用的模式是内插 x4。 这意味着您的最大数据速率为400m/4 = 100MHz。

您正在尝试生成~30MHz 的正弦波。 因此、每个周期只有大约3个点来表示重建的波形。 这就是为什么您在示波器的时域中输出的表现不佳(看起来像噪声)。

这也是为什么、当您将频率降低到~1MHz 时、您会看到输出结构正弦波的更清晰表示。

另一个建议是使用采样400MSPS 时钟的2x 内插、这将使数据速率加倍、并且更准确地表示输出正弦波。 这实际上使每个周期的点数翻倍。

希望这对您有所帮助。

此致、

Rob