请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS114S08 大家好、

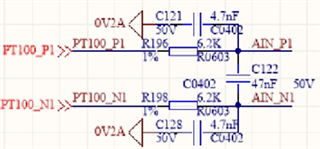

我的客户正在测试 ADS114S08、他们使用6.2k Ω 输入串联电阻和内部基准、输入级原理图如下、增益设置为1。

在测试期间、他们观察到实际增益为1.02、此增益偏移是否由输入串联电阻引起? 如果是、为什么会发生这种情况? 在 ADS114S08功能块中、输入级为多路复用器、我假设多路复用器 FET 的 RDS_ON 不够大、无法导致该增益偏移。 还是由 PGA 输入电阻引起的? 请您对此发表一些评论吗? 谢谢。

此致、

利维亚