在 HART 模式下使用 DAC8742H 时、客户在通过 SPI 读取 Rx FIFO 时遇到问题、尽管它们似乎能够向 Rx FIFO 发送数据并启动 HART 传输。

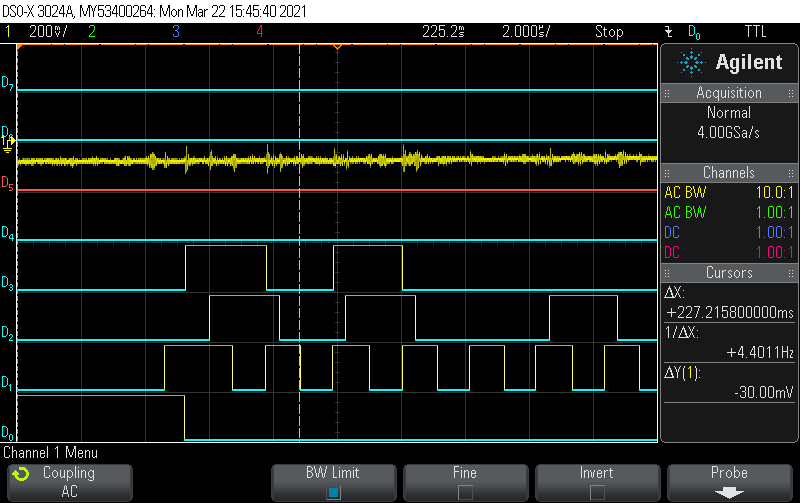

在该系统中、SPI 时钟为~500kHz、连续 SPI 帧之间的间隔大于3usec。 SPI 读取请求间隔为60us、因此这大大超过了 SPI 帧之间所需的最小值2.442us

在 测试 代码中、它们发送两个连续的 MODEM_STATUS 读取请求:0xA00000

在发送第2个读取请求期间接收到的响应是0xA04044、表示 FIFO_M2D 已满、FIFO_D2M 为空。

它们发送4个连续的 FIFO_M2D 寄存器读取请求:0xA40000

收到的答复是:

0x04044

0xA405FF

0xA405FF

0xA405FF

4的第一个是来自第二个状态读取请求的响应。

其他3个响应指示 FULL_FLAG 和 FIFO_LEVEL = 0。 他们假设 FIFO_LEVEL 只是溢出、不能表示16的填充级别。 但是、为什么报告的 FIFO_LEVEL 不会随着每个连续读取请求而递减? 此外、HART 数据字节始终为0xff、而不管它们尝试读取的字节数量如何。