Other Parts Discussed in Thread: ADS7263

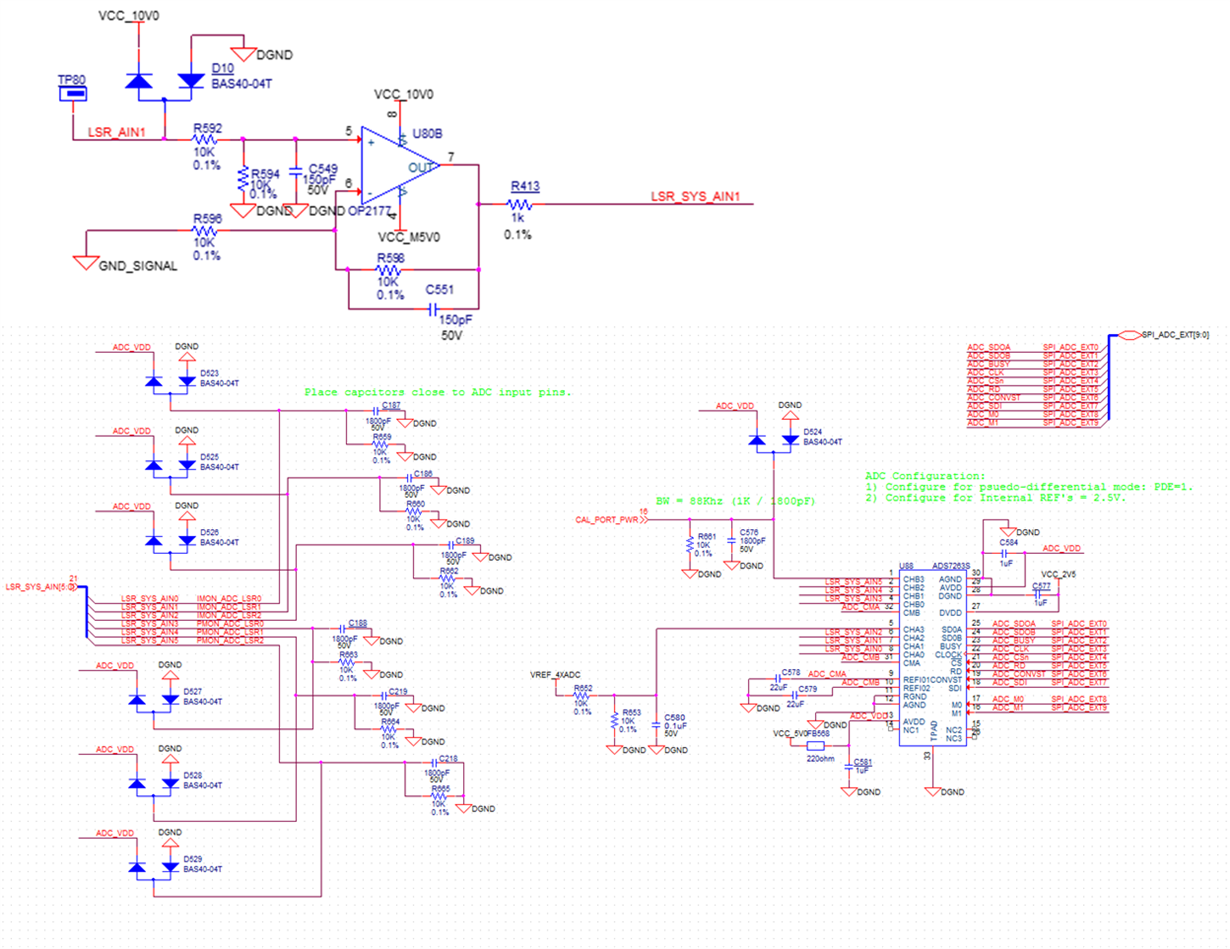

对于我的应用、我将 ADS7263配置为8个单端0-5V 输入通道。 要在单端模式下使用 ADC、REF 输出(设置为2.5V)连接到 CMA 和 CMB 输入。 采样率为每秒250K 个样本。 好消息是、基本功能似乎按预期工作。 唯一的问题是、当实际值为0伏时、每个输入通道上都存在大约0.08伏的大模拟偏移。 输入为2.49伏时的 ADC 值几乎与预期值(半标度)匹配-在0.1%之内。 我已经验证了电源电压(AVDD 为5.0V、DVDD 为2.5V)以及基准电压和共模输入电压值(非常接近2.4999伏)。 虽然0伏输入的视在误差/偏移相对于满量程(大约1%)不大、但我希望误差要小得多。 请看一下、让我知道您是否可以帮助我解决导致大失调电压的原因。