尊敬的所有人:

我使用 ADS5294 ADC 对 ASIC 的输出进行采样。

我们需要对 ASIC 输出多路复用器(阶梯)生成的稳定直流电平进行采样

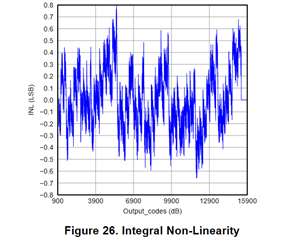

我们担心 ADC 的非线性。

我将 ADC 连接到一个 Kintex7 FPGA、8个模拟输入中的一个连接到一个在 ADC 的全动态范围内摆动的斜坡发生器。

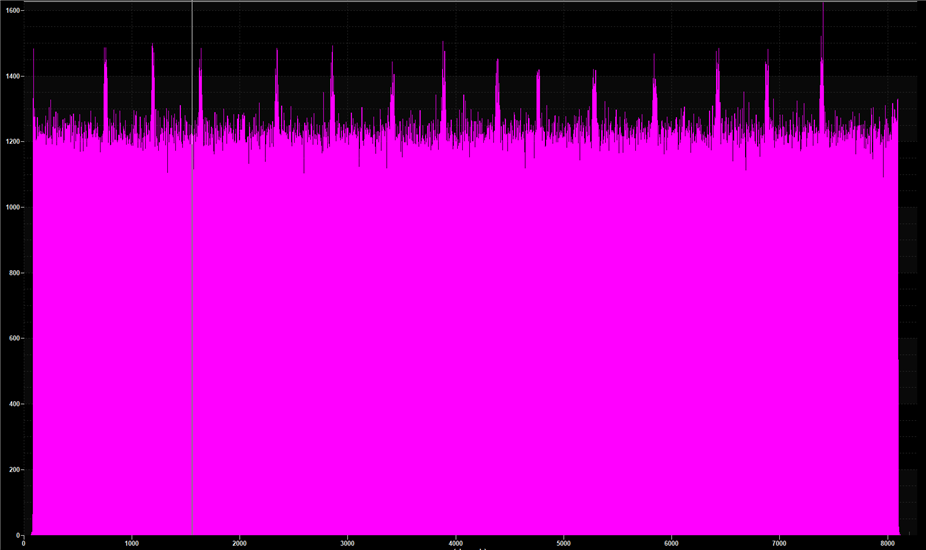

我有一个真正的随机脉冲发生器、可触发 FPGA 对斜坡点进行采样并对其进行直方图。 通过这种方式、我应该生成白分布。

我希望得到一个完美的白分布、但我得到了这样的分布(具有服务器峰值)

ADC 的每个通道的峰值位置不同。

如果我重复此测试、在测试模式中启用数字斜坡发生器(而不对模拟信号进行采样)、我得到的是纯白谱。

ADC 的 INL 看起来会产生这些峰值、但对我来说、影响缝隙太大、无法接受;基线和峰值之间的计数差异约为15-20%。

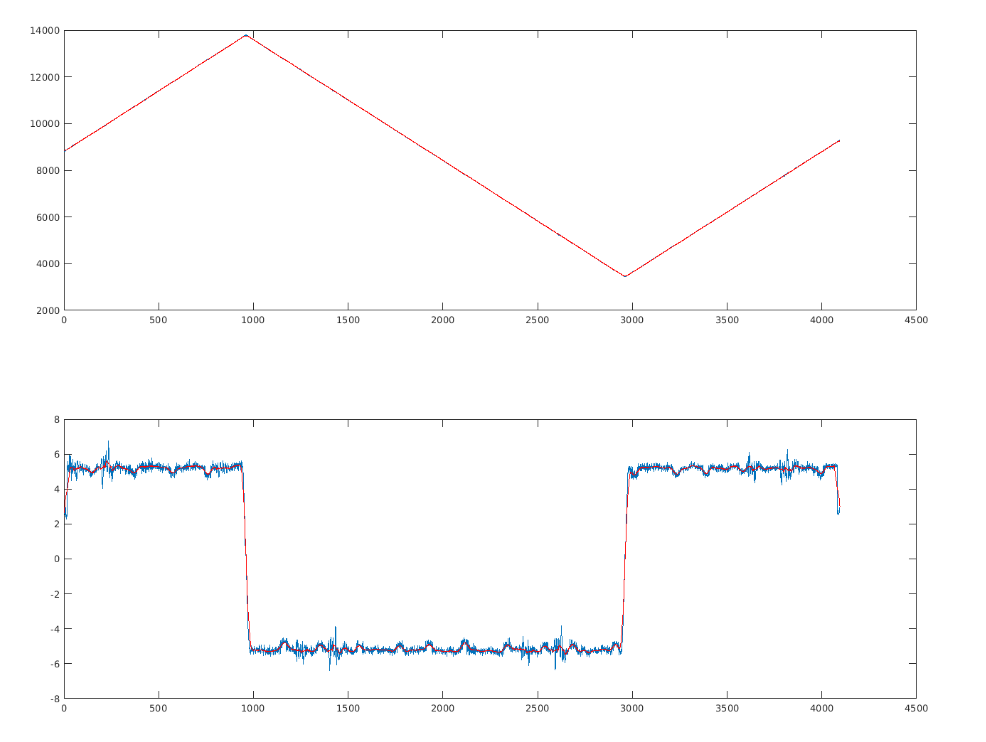

我研究了信号形状。 我采样了一个在0和满量程之间滑动的斜坡波形。 我应用了移动平均法来降低噪声(第一幅图)、并计算了第一幅导数(第二幅图)及其滤波版本(第二幅图中为红色)、我看到导数不是线性的、有一些峰值、每个峰值对应直方图中的峰值

这是该 ADC 的正常行为、还是我们应该调查电路板上的任何问题?

是否有任何方法可以降低这种影响? (不能进行硬件抖动)

谢谢你

Andrea Abba