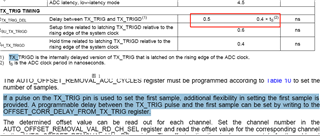

如图1所示,TX_TRIG 的延迟介于0.5ns 和0.4*ts 之间。假设 ADC 时钟频率为62.5M,这将转换为0.5ns 和6.4ns 之间的延迟。显然,这是一个非常长的时间范围, 一个数量级以上、这有时会给计时设计带来麻烦。

继续查看规格、您会发现 TX_TRIG 信号和第一个采样时钟之间的延迟似乎是可编程的、如图2所示。我不知道我的理解是否正确。如果它是可编程的、 8位 OFFSET_CORDELAY_FAND_TX_TRIG 寄存器和 DELAY 之间的对应关系是什么?在规格中未找到这一点。

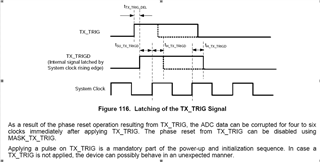

如下图所示、当系统时钟信号连续两次接收 TX_TRIG 信号时、将立即销毁4-6个时钟数据。可以使用 MASK_TX_TRIG 寄存器禁用相位复位。不知道我的理解是正确的吗?

除了 TX_TRIG 信号和系统时钟之间的时序限制外、还有哪些其他限制?

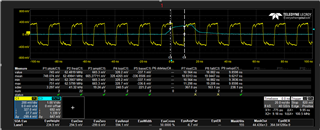

下图显示了在电路板卡 AFE58JD28引脚处测得的 TX_TRIG 和系统时钟之间的时序关系。 它是否满足时序要求?随着温度变化和器件之间的差异变化、时序是否仍然满足要求?