主题中讨论的其他器件: LMK04828、

您好!

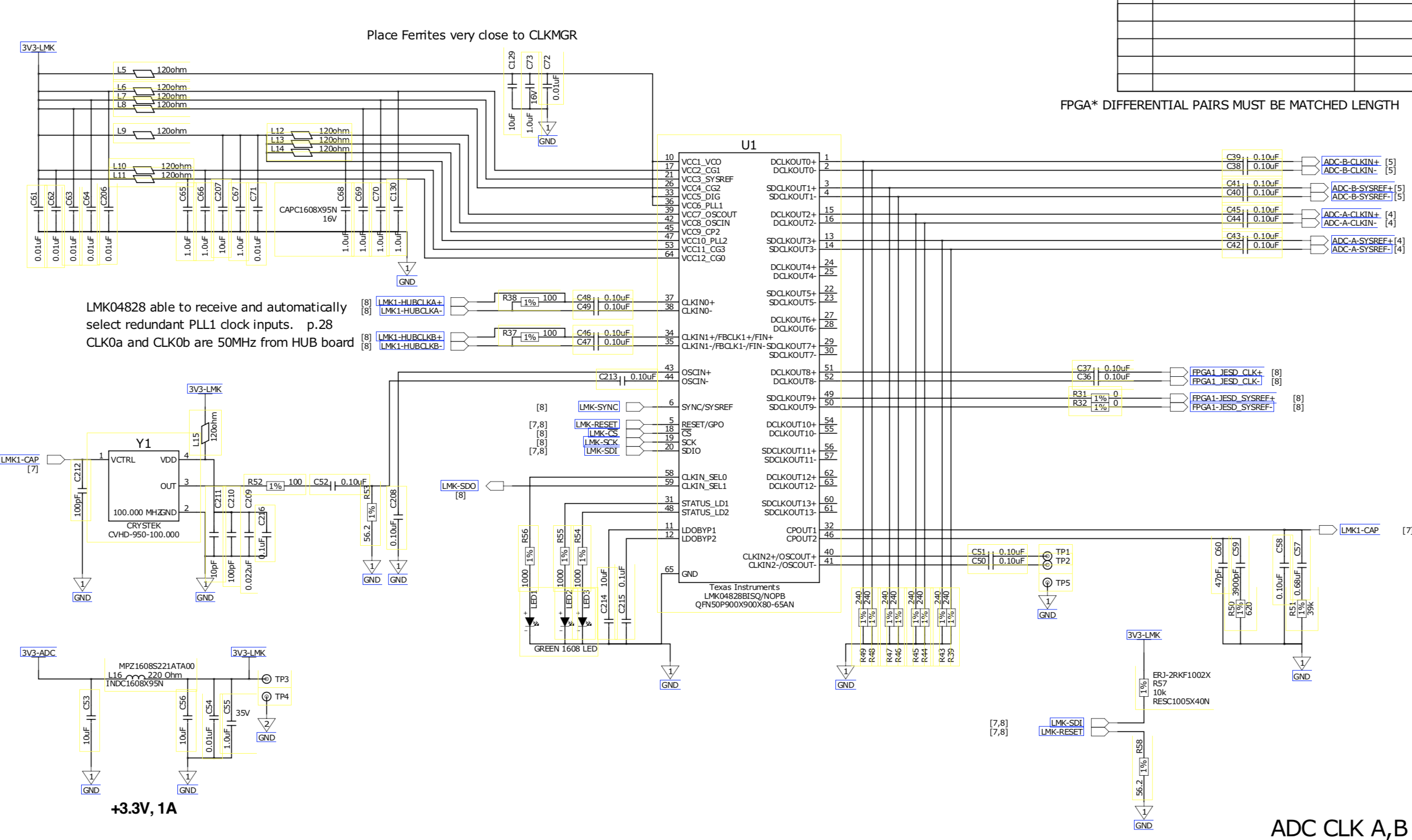

我们有一个托管两个 ADS54J66的定制 PCB。 对于其中一个 ADC、我们在所有情况下都观察到预期行为、我们可以 通过 SPI 配置并读回配置、所有内容都是一致的。 另一个 ADC 的行为也不一样。 它的配置足够好、可以实现 JESD 同步、但对于启用测试模式和/或关闭交错校正等操作、ADC 的响应不一致。 读回值永远不是它们应该具有的值、并且可能会相当不一致;有时您会看到值与预期值只有一位差、有时错误的寄存器会读回预期值。 例如、如果我使用 值0x40对 ADC 页寄存器0x0F74进行编程以启用测试斜坡、有时我可以在寄存器0x0F6D 中看到值0x40。 对每个 ADC 进行编程和回读时使用相同的代码。 我还使用了相同的代码对 ADS54J66EVM 上的 ADC 进行编程、没有问题。 我还使用示波器探测了 ADC 上的 SPI 信号、以确保它们看起来正常、确实正常。 这不仅是回读问题、我也无法让该 ADC 执行 JESD 数据扰频或进入测试斜坡模式。

该定制 PCB 有两个副本、每个副本有两个 ADC - A 和 B。在每个 PCB 上、ADC-A 显示奇怪的 SPI 行为、ADC-B 行为良好。 但是、对于其中一个 PCB 、ADC-A 有时会正确读回某些寄存器、而对于另一个 PCB ADC-A、基本上不会正确读回任何内容。

在每个 PCB 上、ADC 共享所有电源轨、因此似乎不太可能出现问题 的原因是电源轨不可靠。

我已经对这个问题进行了调查、我相信这个问题在 ADC 芯片内、 除了 两个不同 PCB 上的 ADC-A 显示出类似的意外行为。 这似乎表明每个 PCB 上的该芯片应该存在一些系统问题。 我们花了很多时间来研究与 ADC-A 和 B 相关的 PCB 布局和设计、尝试提供合理的解释、说明哪些可能会导致观察到的编程问题、到目前为止我们 没有发现任何问题。 在我们的设计中、两个 ADC 的处理方式几乎相同。

现在、我们可以实现与 ADC 的同步并可靠地读取数据、因此核心 ADC 功能似乎可以正常工作、但我们没有足够的信心在这个悬而未决的问题未得到解决的情况下继续进行我们的设计。 如果可以避免、我们更愿意避免更换电路板上的芯片、因此我希望这里的人能告诉我是否有任何我可能忽略的东西可以解释我们看到的行为。 或者、如果有一些测试可能指示此问题的来源。 或者、如果人们过去看到过类似的问题。

我很高兴分享一些设计文件/屏幕截图或我提到的问题的具体示例、如果这样做有帮助的话。

谢谢、

Eric M