您好!

我们使用 的是 DS90UB948-Q1、数据速率高达3.4Gbps、 我们的示波器不足以运行眼图、您还有其他方法可以评估 FPD 链路的信号质量吗? 或某种裕度分析方法?

如果有、请提供详细信息...

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们使用 的是 DS90UB948-Q1、数据速率高达3.4Gbps、 我们的示波器不足以运行眼图、您还有其他方法可以评估 FPD 链路的信号质量吗? 或某种裕度分析方法?

如果有、请提供详细信息...

张您好、

是的、您可以使用 我们的地图工具。

确保您已从 此处安装了最新的 ALP 工具、之后是配置文件更新程序、以便能够使用地图工具

感谢您提供有关 CML 端口的信息、我还注意到 CMLOUT0和 CMLOUT1在测量方面的差异;

正确、100MHz 对于948无效、我将在测试中纠正这一点;

但对于抖动、很抱歉、我的描述不够清晰、实际上、我在 CMLOUT 上和直接在电缆上进行了测量、但发现了明显的差异;

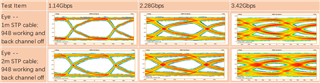

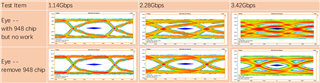

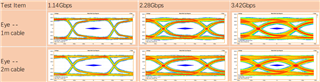

分享以下图片、这些图片是电缆的测试结果、无论设备的带宽限制如何、都可以知道:

1) 1) CMLOUT 在同一设置下无法获得相同的性能;

2) 948芯片正在发挥重要作用、电缆的冲击除外;

3) 3) PCB 布线对其几乎没有影响。

基于这些结果、这就是我在测试 CMLPORT 时需要考虑的原因。