Other Parts Discussed in Thread: DAC63004, DAC63204, ENERGIA, DAC53204, ADS7953

主题中讨论的其他器件:DAC63004、 ENERGIA、 DAC53204、 ADS7953

您好!

我想将 DAC 与 NVM 和多通道 ADC "结合"在一个 SPI 接口上。

对于这种情况、其中一个应在第一个数据包(? 位)和其他位应忽略该位并在相同的/CS 期间响应最后一个数据包(可能具有不同的长度)。 如果我要找到这样工作的器件、一切都应该正常工作。 今天、我有这样的安排、不是 TI 器件、而是 DAC 中没有 NVM。 SAR ADC 首先锁定8位并立即响应(在相同的/CS 期间)结果、DAC 等待直到/CS 的结束(上升)、并将最后一个数据包作为命令(即使采用 NOP 选项)。

我还需要 ADC 和 DAC 在不活动/CS 期间处于完全静音模式。

现在,使用新的 DAC 器件,内部有 NVM,我想升级功能并获得相似的性能,但这些 DAC 在应用/CS 后对第一个 x 位作出响应,这使我完全丧失了乐趣:-)。

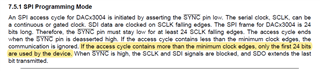

这来自 DAC63204/DAC63004数据表、第27页:"如果访问周期包含的时间超过最小时钟边沿、 器件只使用前24位。"

请提供建议。