大家好、

我们的客户希望仔细检查启动脉冲的周期。

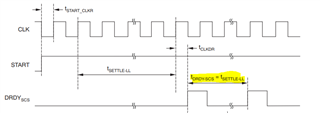

在单周期稳定配置中、START 脉冲的周期大于 tSETTLE。 它不包括 DOUT 24位数据输出的周期(1.2us@fclk = 20MHz)。

是这样吗?

他们认为、如果 DRDY 置位、转换数据将保持不变。 但是、即使在单周期稳定中、如果在将 DRDY 置为有效之前再次将 START 置为有效、则数据也将被清空。

谢谢、此致、

米希亚基

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们的客户希望仔细检查启动脉冲的周期。

在单周期稳定配置中、START 脉冲的周期大于 tSETTLE。 它不包括 DOUT 24位数据输出的周期(1.2us@fclk = 20MHz)。

是这样吗?

他们认为、如果 DRDY 置位、转换数据将保持不变。 但是、即使在单周期稳定中、如果在将 DRDY 置为有效之前再次将 START 置为有效、则数据也将被清空。

谢谢、此致、

米希亚基

您好 Michiaki、

输出数据周期或总启动周期将长于 tSETTLE。 START 脉冲宽度必须至少为1个 tCLK 周期、然后等待 DRDY 从低电平转换为高电平(tSETTLE)、然后从器件输出时钟数据结果。 之后、您可以发出另一个 START 脉冲。

单周期稳定可导致稍快的输出数据速率、另一个选项是将 START 引脚设置为高电平并保持高电平、等待 DRDY 的上升沿(tSETTLE)、为数据计时、然后等待下一个 DRDY 上升沿。 在这种情况下、输出数据速率周期将为 tSETTLE、如图25所示。

此致、

Keith Nicholas

精密 ADC 应用