主题中讨论的其他器件:SN74LVC1G06、

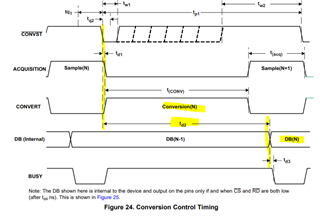

我需要将32个 ADS84221连接在一起(引脚36 BUSY)。 我希望获得该输出的确切规格。

这32个引脚将连接在一起并连接到 FPGA Cyclone 5 (Altera)的一个引脚。

最好的方法是提供一些原理图建议、以便能够连接所有这些引脚、并且一个组件只能构建一个忙信号。

我已经使用了一个简单的二极管(阳极到引脚36、所有阴极都短接)连接到每个 ADS84221、但我不喜欢这个解决方案。

如果您有任何关于此主题的应用手册、我们将不胜感激。

信号 BUSY 用于 Altera 的 FPGA Cyclone 5。

感谢你的帮助。