主题中讨论的其他器件:ADS1274、

尊敬的 TI 社区:

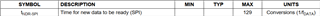

我对 ADS1274/8数据表的表10有一个简单的问题。

这是否意味着/DRDY 稳定时间为129 *(1 / Fdata)?

例如、对于 Fdata = 1kHz => tNDR-SPI = 129ms

感谢你的帮助。

此致

Benjamin Nordman

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Benjamin、

我将帖子标题更新为 ADS1274。

这与模式更改类似。 如果您以1ksps 运行并将/SYNC 引脚置为有效、则会重置数字滤波器、并且需要129次转换或129mS 才能查看下一个/DRDY 并检索下一个转换结果。 在该初始延迟之后、当/SYNC 保持高电平时、您将以1ksps 速率或每1ms 获得一次数据。

此致、

Keith Nicholas

精密 ADC 应用