您好!

我开始研究"slac748_adc12dj3200_A10fpga_jesd204b_fher_TI"、源代码和用户指南等

我注意到、用户指南和源文件之间的 JESD204B 配置看起来不同、其中源文件使用 Quartus Prime Pro 16.1版还原。

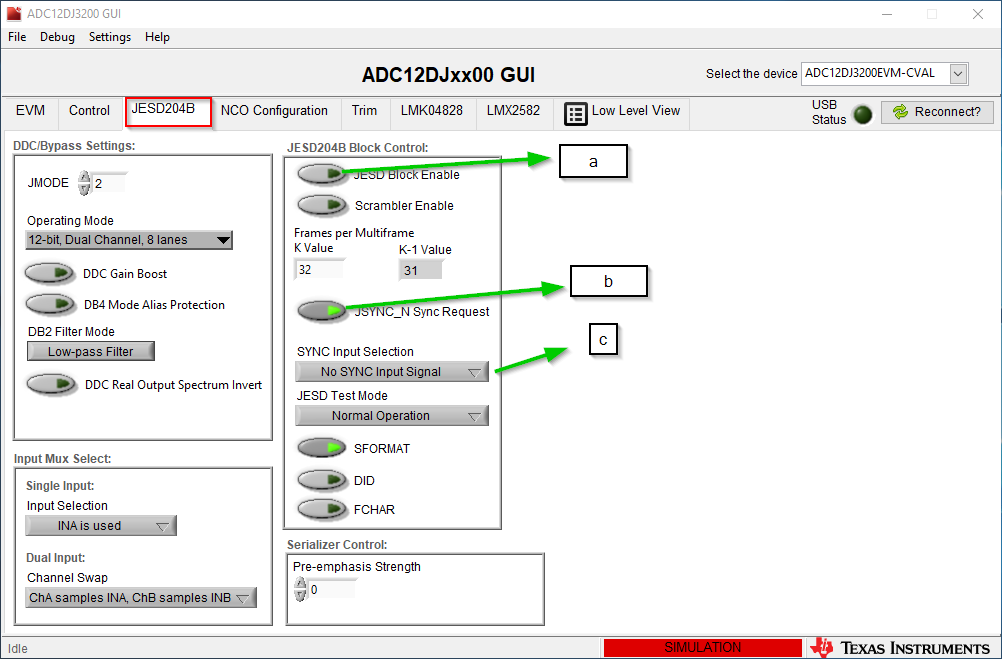

例如,在配置 ADC 的用户指南中显示 K=4,但在"altera_jesd2041_....中显示 K=32 V"、见下文。 以下值与 Qsys 设置匹配。

Altera_jesd2041_altera_jesd204_161_kzbcg4i #(

.device_family ("Arria 10")、

SUBCLASSV (1)、

PCS_CONFIG ("JESD_PCS_CFG2")、

.L (8)、

.M (4)、

.F (1)、

.N (16)、

.N_PRIME (16)、

.S (1)、

.K (32)、

SCR (1)、

.CS (0)、

CF (0)、

.HD (0)、

ECC_EN (1)、

.DLB_TEST (0)、

我的问题是:

问1、是否应使用 K =32或 K =4? 如果不同、也有其他参数。

此外、在用户指南中、它指出"在此 EVM 版本中、上四个 SERDES 通道的 P 和 N 引脚交换、因此在设计中实现了 Rx 通道极性反转以解决这一问题。" 所以、

Q#2、哪个 FPGA 模块或块对其进行寻址。

希望尽快收到消息。