您好!

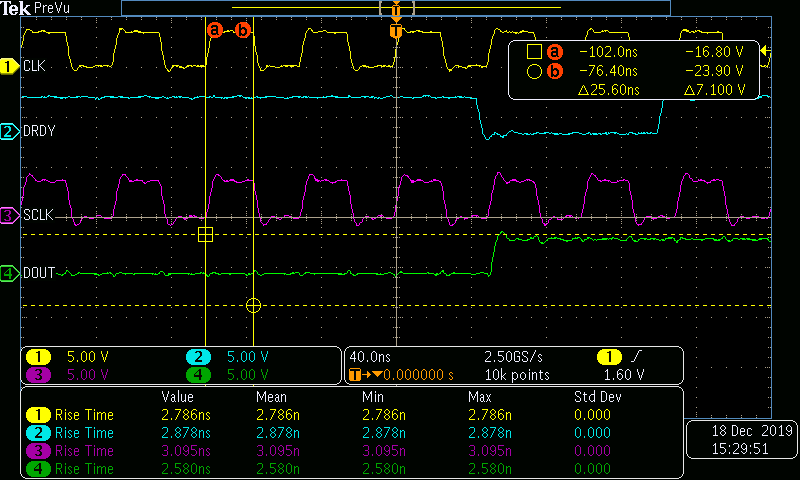

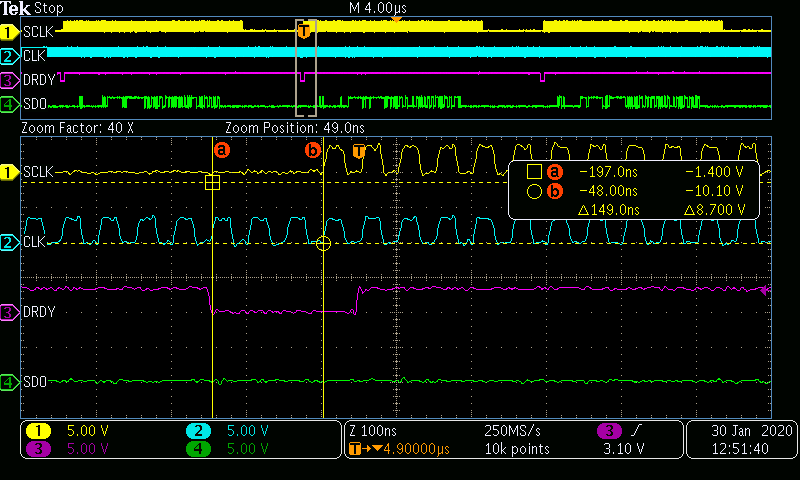

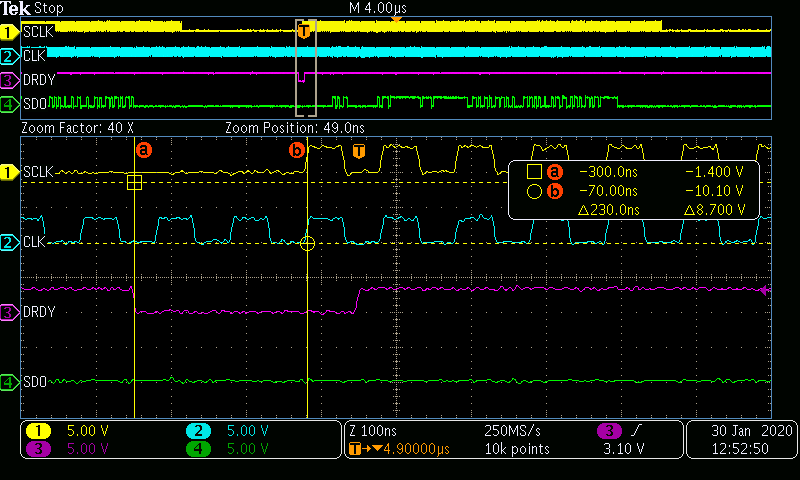

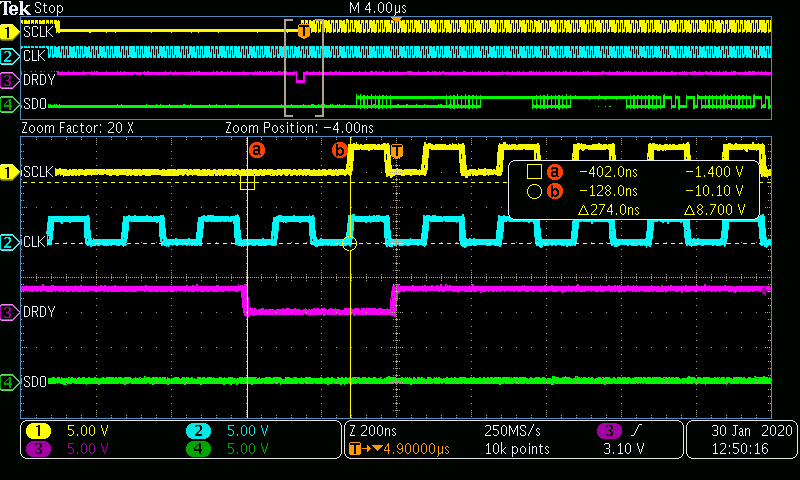

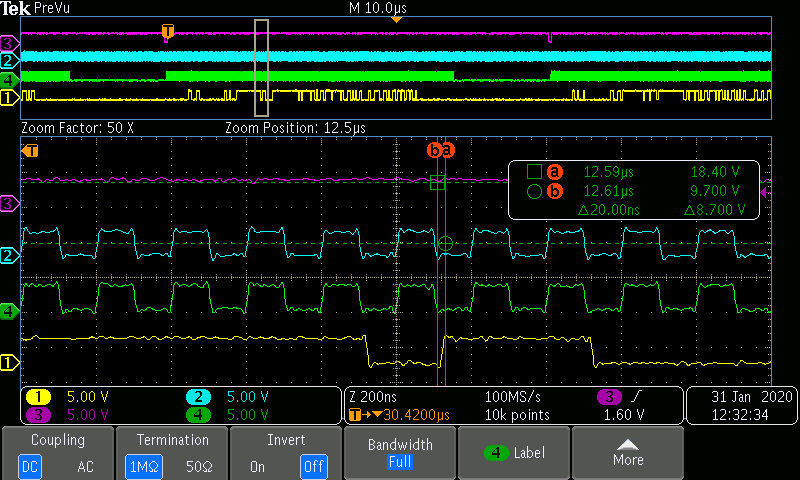

当 SCLK / CLK 设置为20MHz 时、我在准确读取数据时遇到问题、但当时钟频率为5MHz 时、读取数据时会准确。

此外、当我在 SCLK 或 DOUT 线路上进行探测时、ADC 数据似乎正常。

探头电容有助于在 SPI 时序特性中调整时序延迟。

我构建了9块电路板、发现5块电路板在20MHz 下无缝工作、所有电路板在5MHz 下工作。

需要了解设计中的最佳解决方案是什么才能实现一致的性能。

???? 目前的设计只有串联端接、没有 RC 配置、建议如何改进设计???????

通过将低通 RC 串联、减少 SCLK 中的纹波也解决了这个问题。

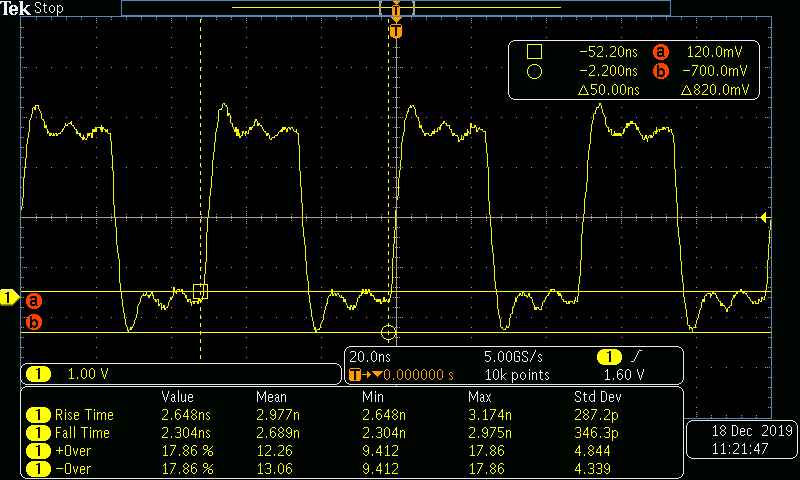

SCLK 范围排除:

ADS1278中的电流配置为 SPI 和 TDM 模式、使用7个有效通道。

感谢您帮助解决此问题。

谢谢、

Mani