在使用 ads5560期间、我们的 KMM 客户会遇到以下问题。 请帮助回答这些问题

1、μ A 时钟是采用 FPGA 的差分时钟输出、还是仍然需要使用特殊的时钟芯片来形成全差分时钟?

2、由控制引脚 SEN 控制的输出时钟的延迟与哪个信号被延迟(输入时钟、或者输出数据?)相对应?

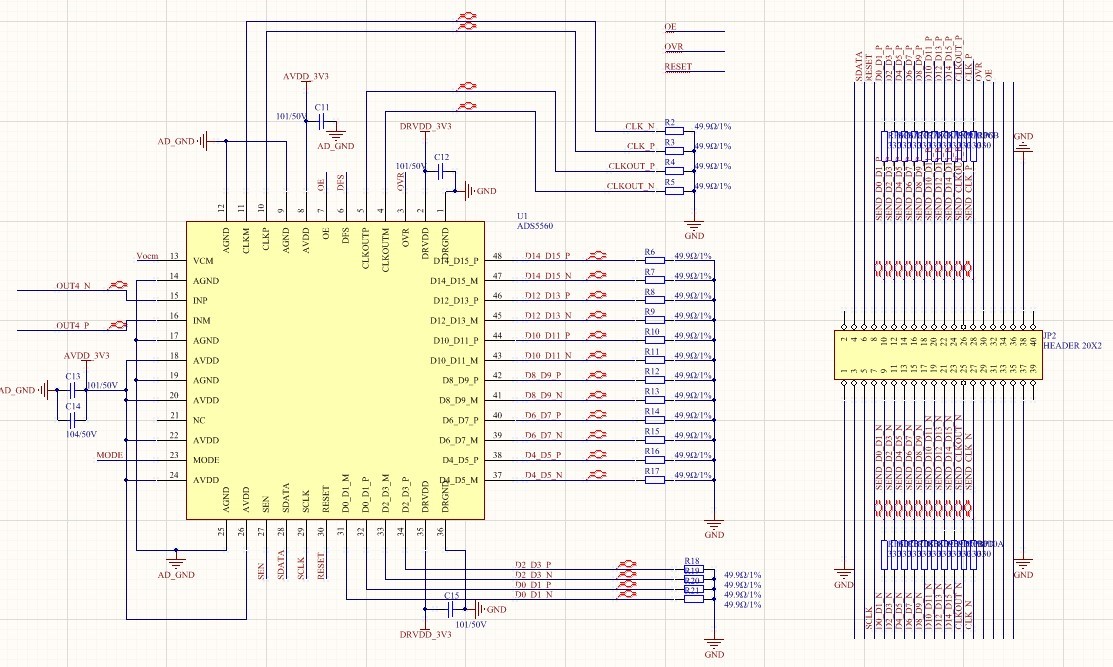

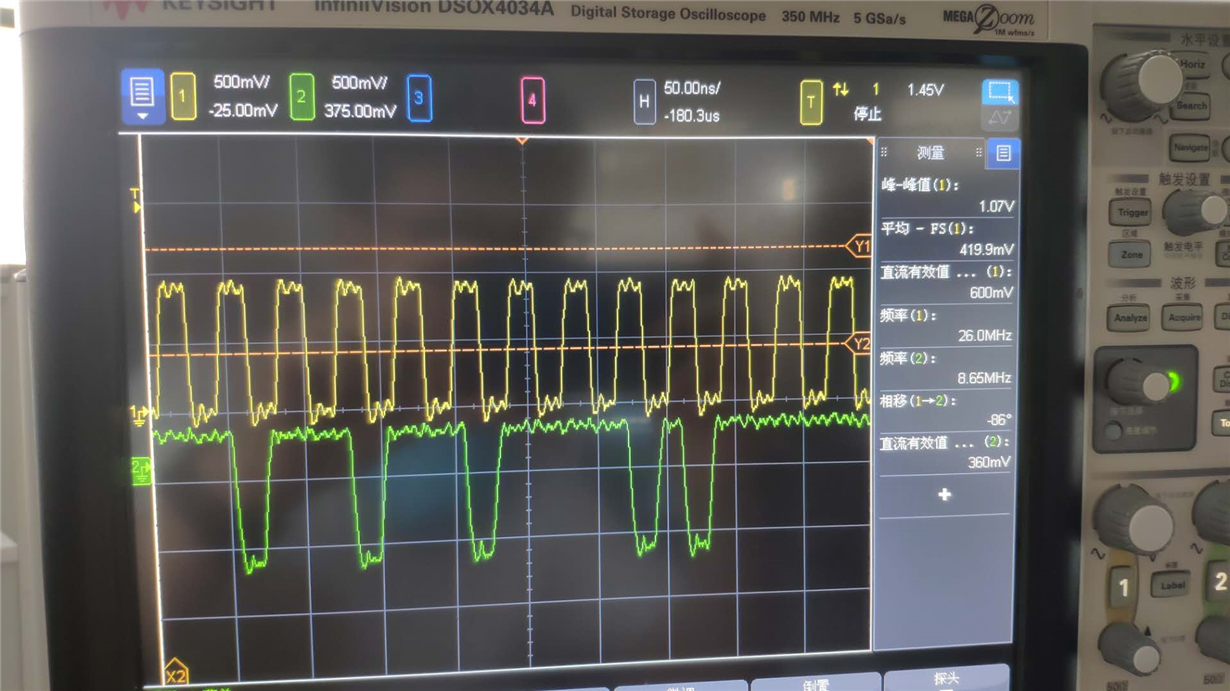

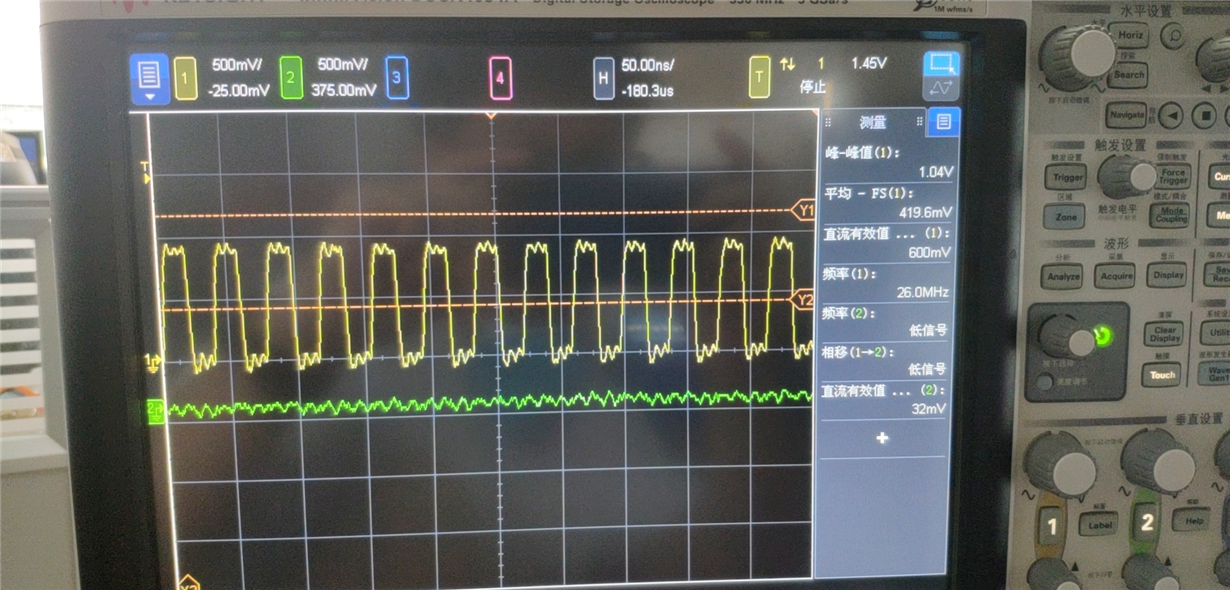

3、 应使用哪种匹配方法来匹配数据输出引脚的阻抗。?我们当前使用的匹配方法是在输出引脚和 GND 之间连接一个50Ω Ω 电阻器。电路板的匹配电路如下:

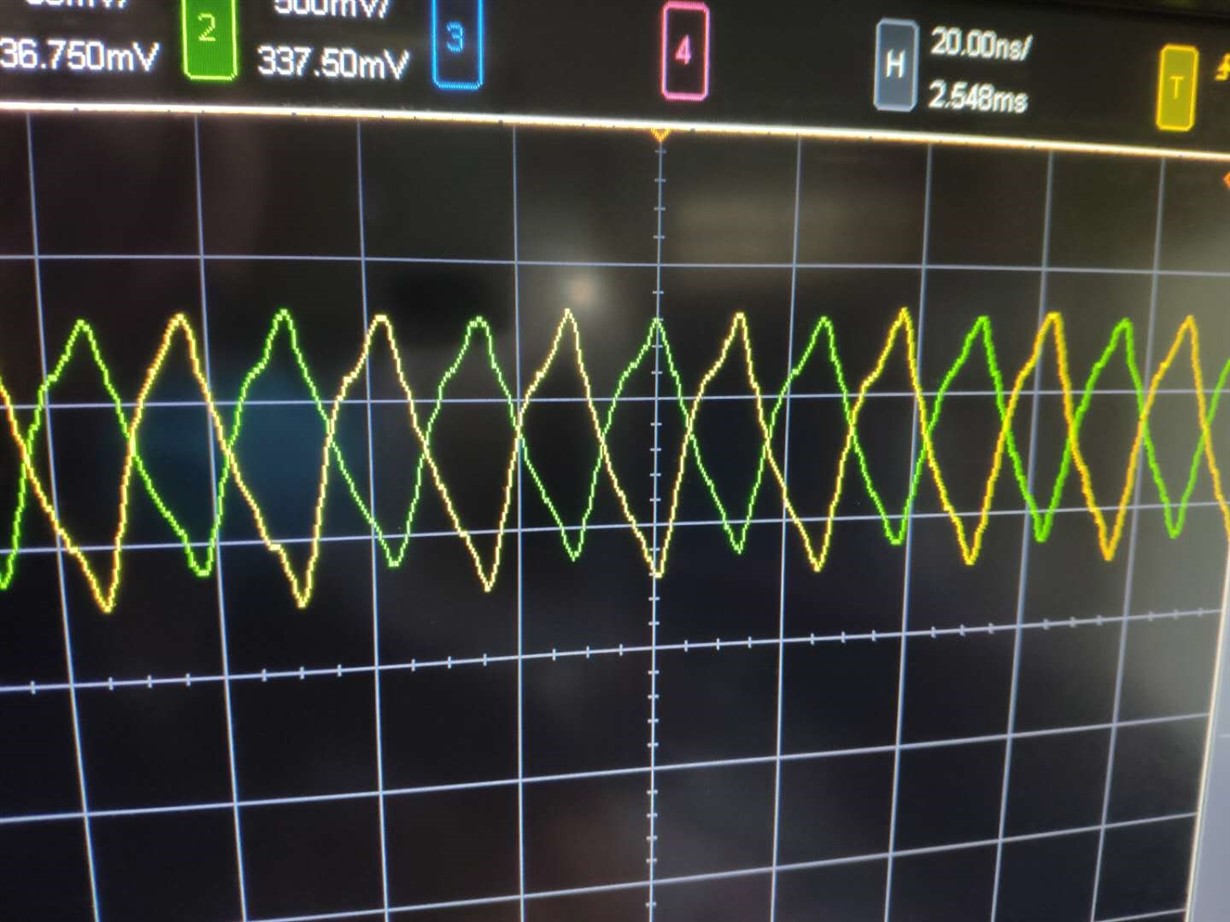

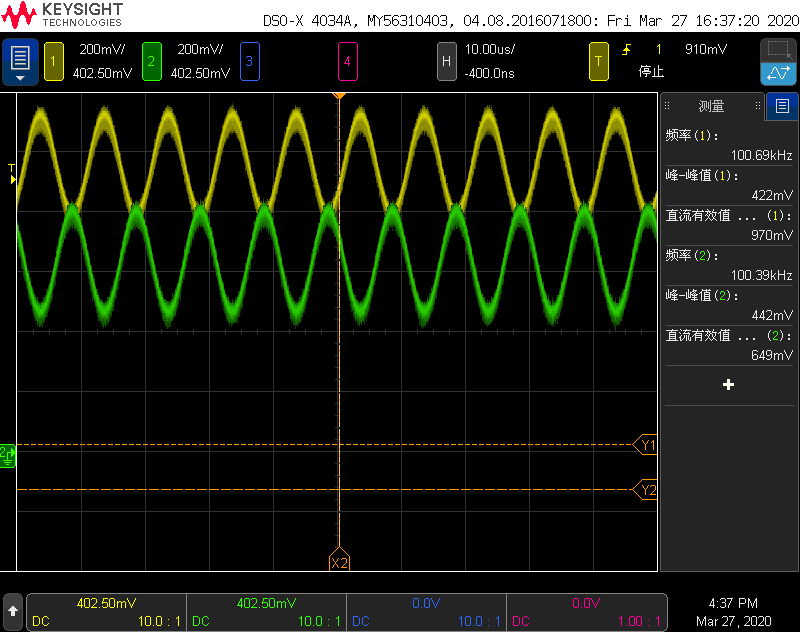

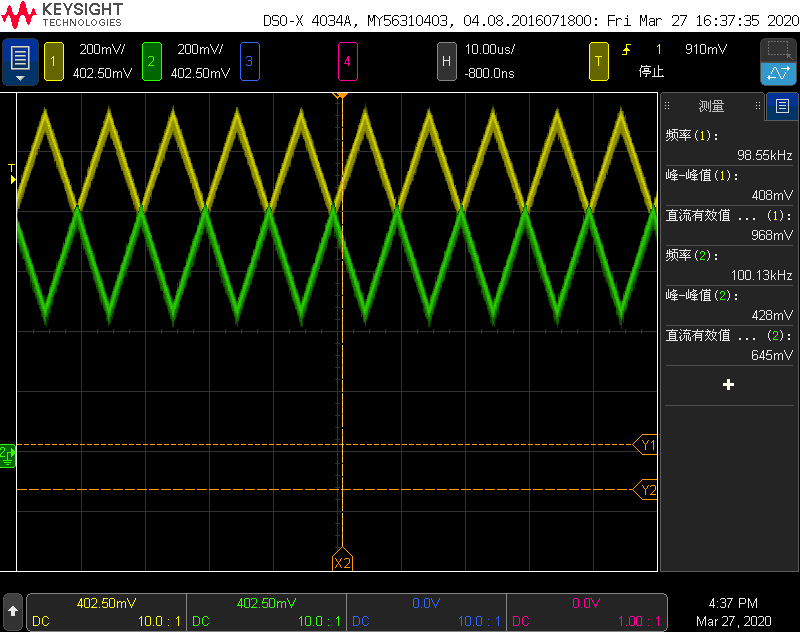

B、匹配后的波形:

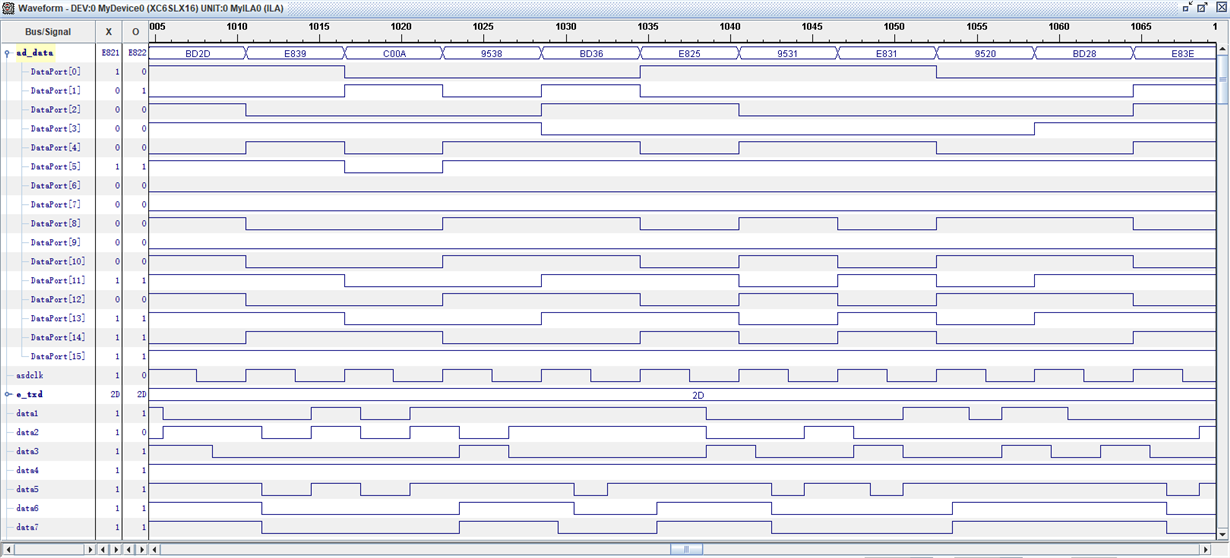

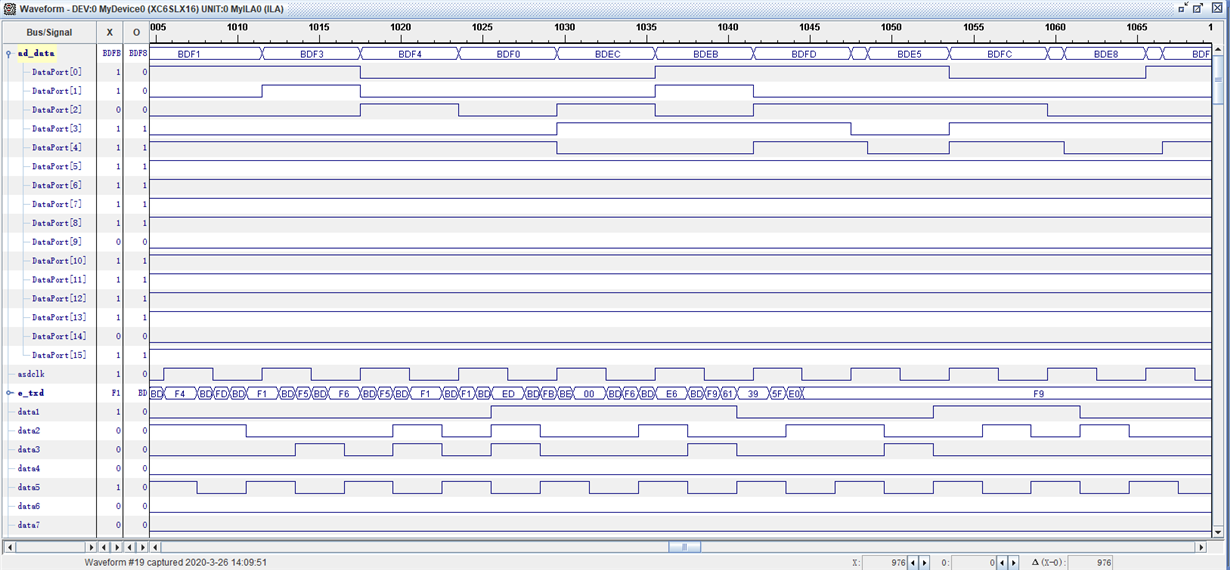

4 μ s 在、FPGA 时、您能否为 ADS5560提供一些数据处理例程?

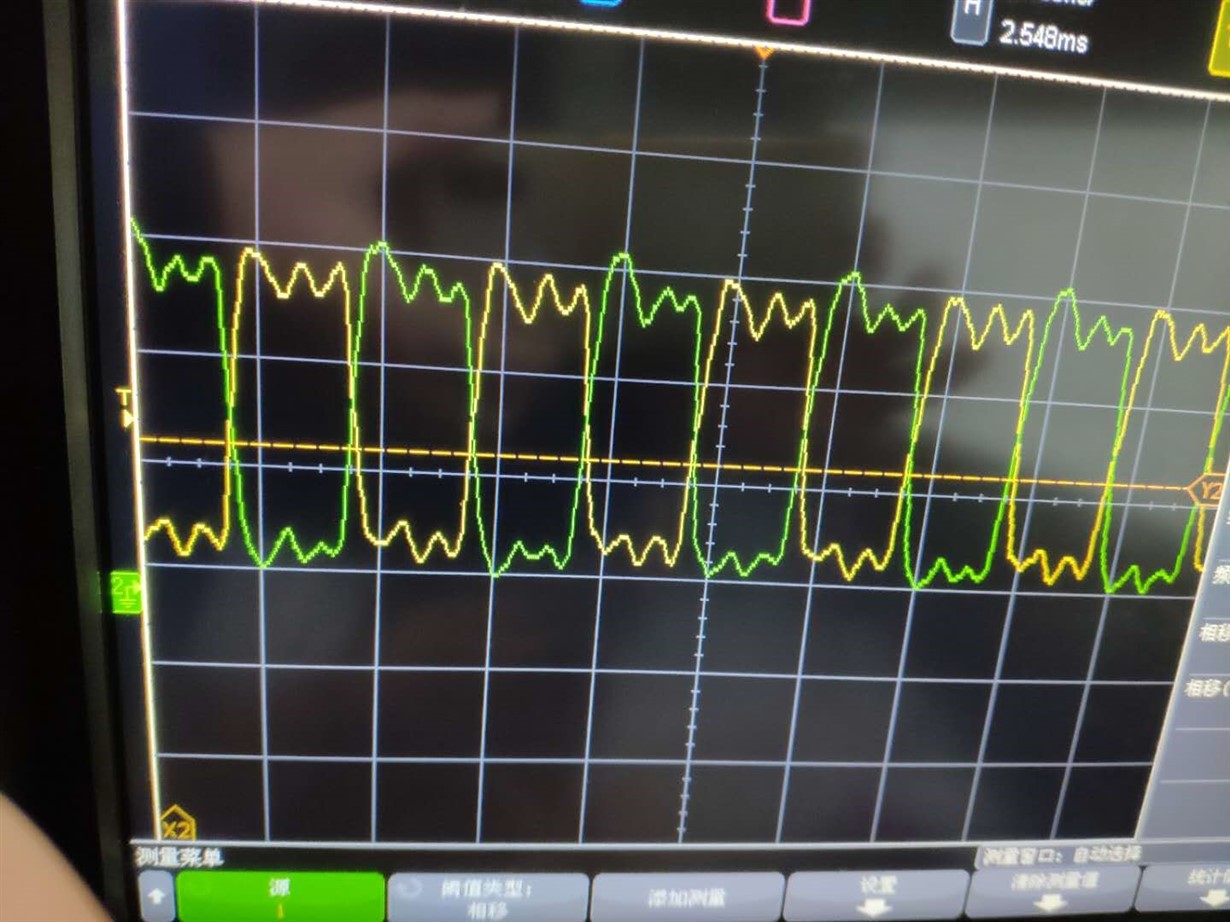

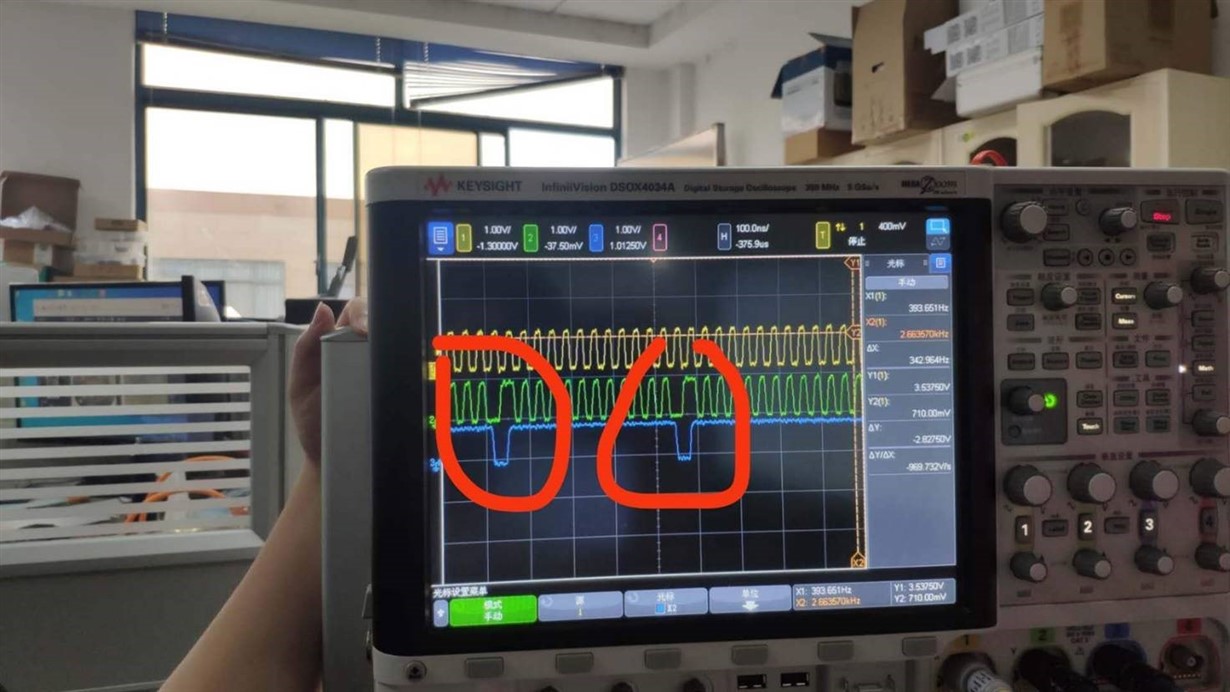

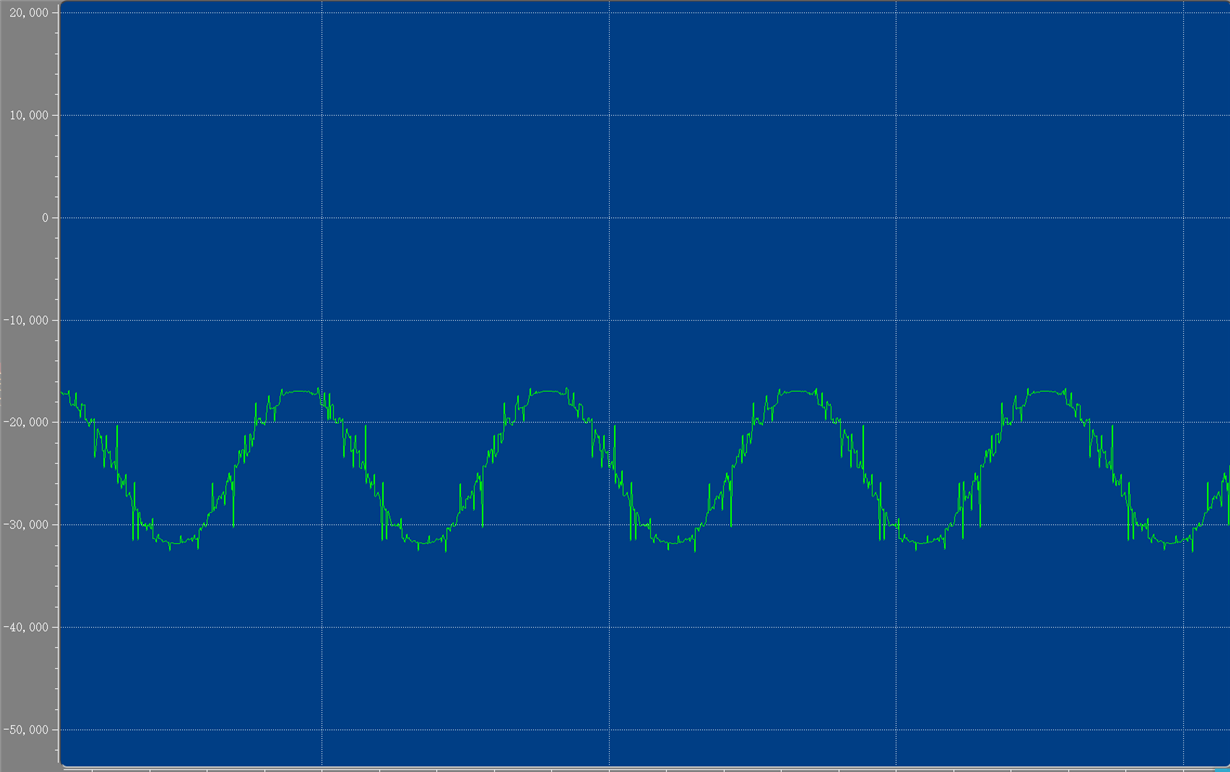

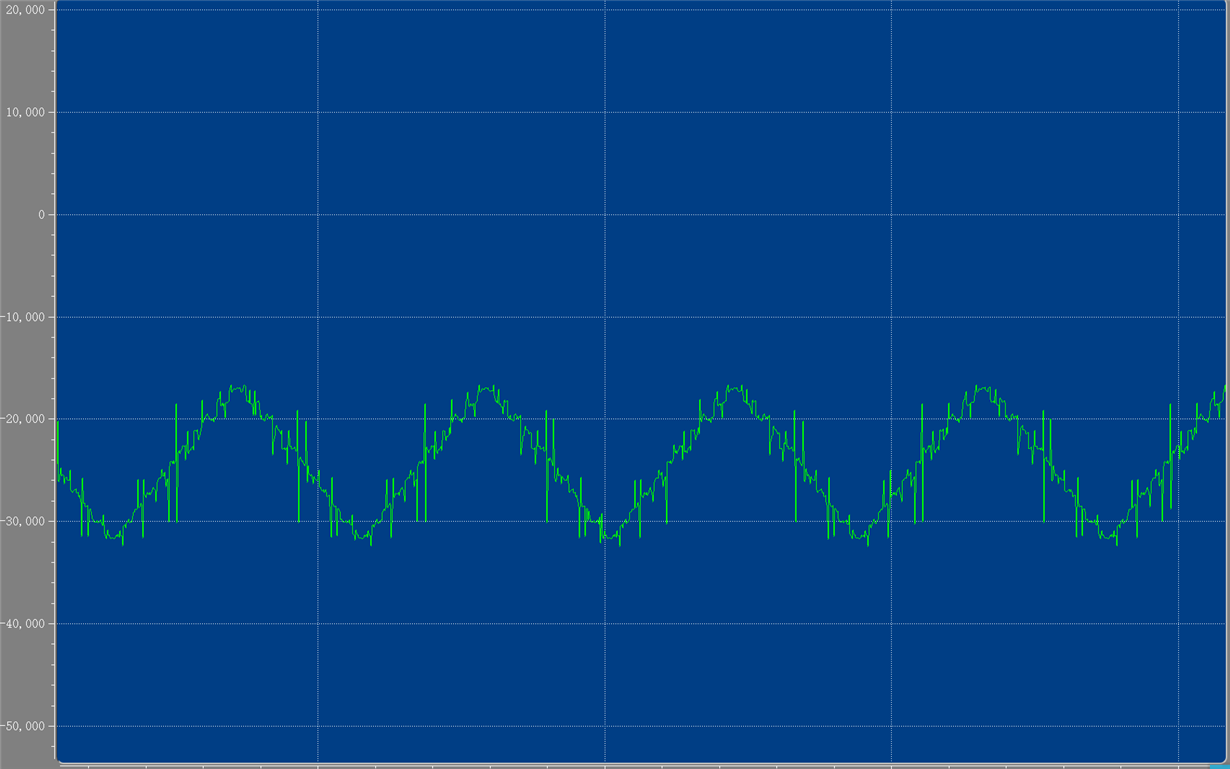

5 μ s、、我们比较了电路板和 ads5560evm 之间的差异:电路板使用 FPGA 的差分时钟输出、而 ads5560evm 使用特殊时钟芯片的时钟输出。 我们始终将输入连接到 GND、并对数据14和数据15 (pin47和 pin48)进行采样。 有时、我们可以捕获1的信号、如下图所示、这会导致采样数据出现尖峰。 我不知道这是不是因为时钟信号?