您好!

我尝试在6GSPS、 4总线、交错模式时序的单通道模式下使用 ADC12DL3200进行设计(LDEMUX = 1、DES_EN = 1、LALIGNED = 0)、如数据表图6所示。 ADC 使用外部输入器件时钟3GHz、并在 ADC 上电之前保持稳定。

现在、我可以通过 SPI 正确访问所有寄存器、我按照数据表8.3部分的初始化设置来初始化 ADC。

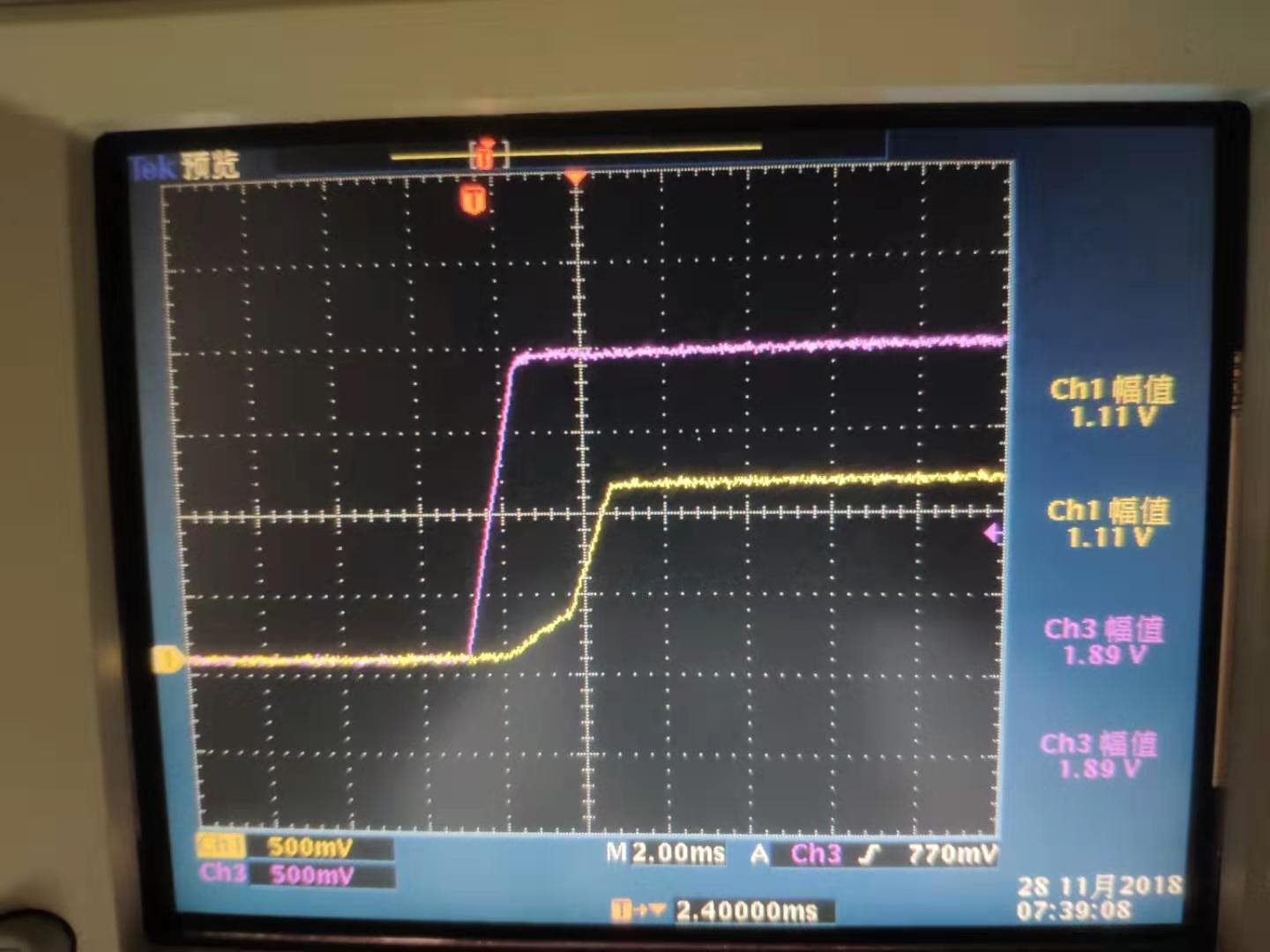

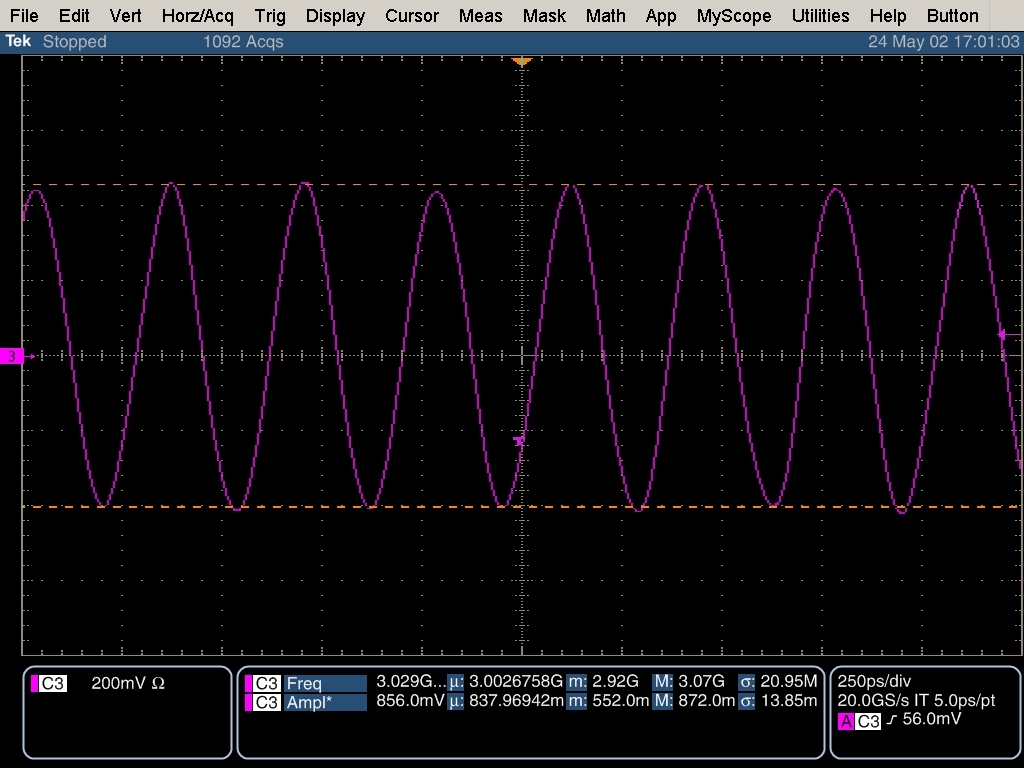

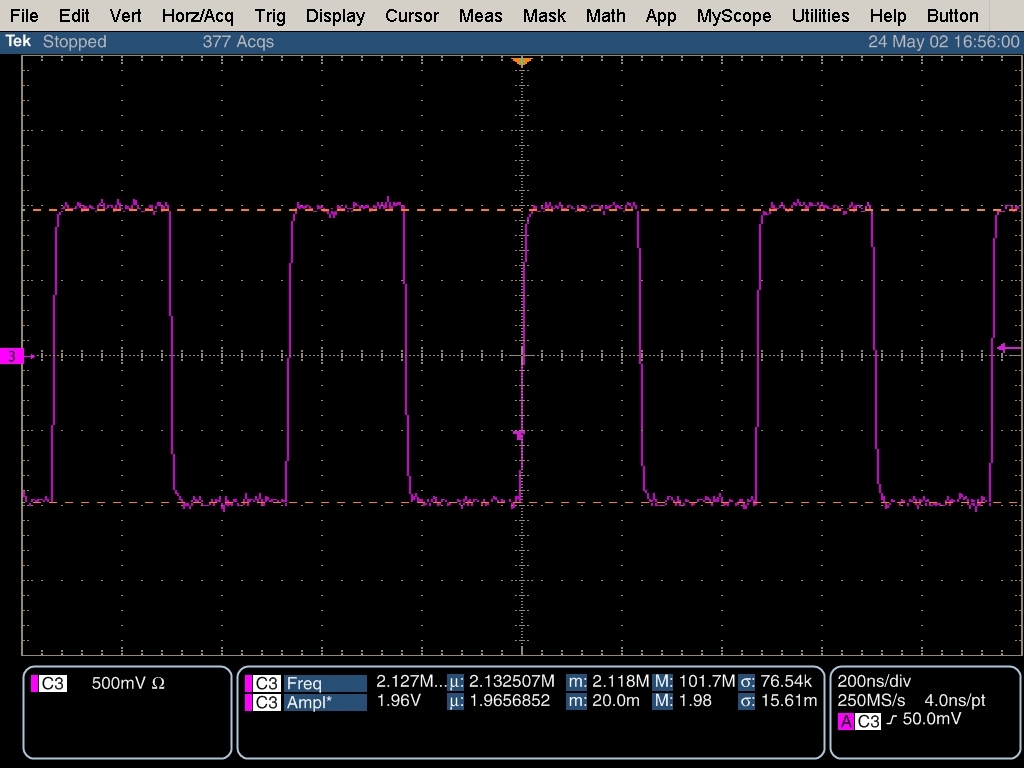

但在 FPGA 侧、我无法锁定 DxCLK、我在电路板上使用高速示波器测试了 DxCLK、这让我感到惊讶的是、所有4条 LVDS 总线的频率 DxCLK 都是~2.12M、而不是我想象的750MHz。 2.12MHz 时钟在 SI 非常好的情况下保持稳定。 并且即使没有启用3GHz 设备时钟 或下载 FPGA 固件,此时钟也会在加电后显示。(等于断开所有 SPI/LVDS 与 FPGA 的连接)。

由于我的项目中仅使用单个 ADC、因此未提供 SYSCref/TMSTP。

您是否认为 DxCLK 运行正常? 为什么是2.12MHz? 如果行为不正确、是否有进一步调试这种情况的建议?

非常感谢。