主题中讨论的其他器件: DDC264

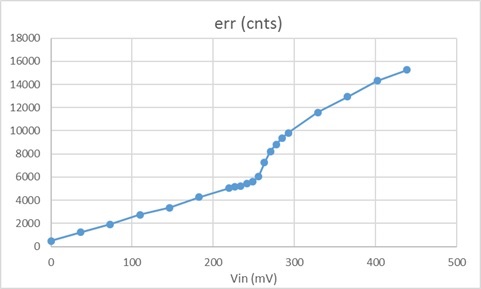

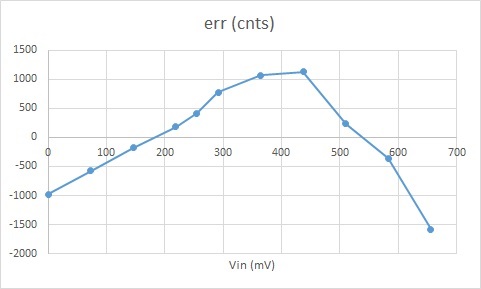

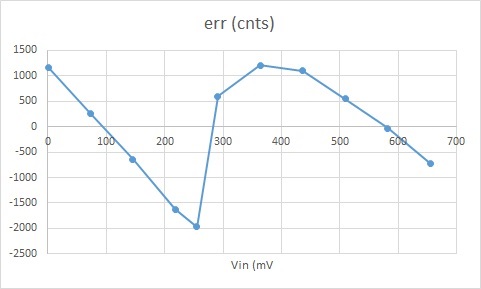

DDC118线性问题–如测试数据图(图1)所示。 问题是、DDC118线性在输入信号中间有突然变化。

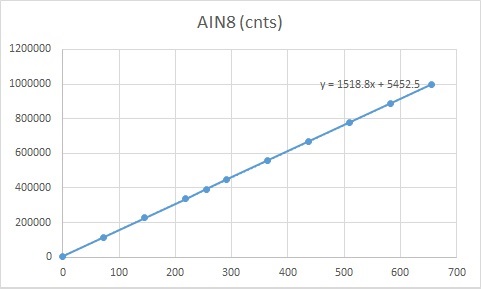

测试是使用测试电路完成的、如图 2.向电阻器 RT 施加恒定电流源 IC (7.31uA)。 则缓冲运算放大器输出电压为 IC*RT。 10Mohm 电阻器将电压转换为电流输入、然后再转换为 DDC118输入之一。 对于不同的 RT 电阻值,记录 DDC118计数并将其转换为测量电阻,并将其与真实 RT 值进行比较,以计算出测量误差--图的垂直轴。 DDC118设置为:范围111、集成时间5ms。 在该设置下、线性变化发生在 ADC 计数约为400、000 (RT = 35k Ω 至40k Ω)时。