Other Parts Discussed in Thread: DAC121S101

我使用 DAC121S101来生成正弦波。

通过查找表读取正弦值、当写入输出时、可以在输出上看到非常糟糕的毛刺脉冲、如下所示。

使用分析仪、我查看了发送到 DAC 的数据、下面显示了这些数据、而不是仔细查看其中的一些干扰、 数据似乎与 DAC 输出中的毛刺脉冲不一致、因此我相对地确定误差是在 DAC 内引起的、并且发送的数据正常。 下面是写入 DAC 的值的错误快照。

这里的 DAC 输出是蓝色迹线、十六进制值表示正在写入 DAC 的数据。 这些是使用 DAC 引脚上的示波器记录的。 很明显、数据在不断减少、但 DAC 输出有时会增加。

需要注意的其他一点是、电源/基准电压看起来非常干净、SCLK 频率为20MHz。

VA 为+5V。

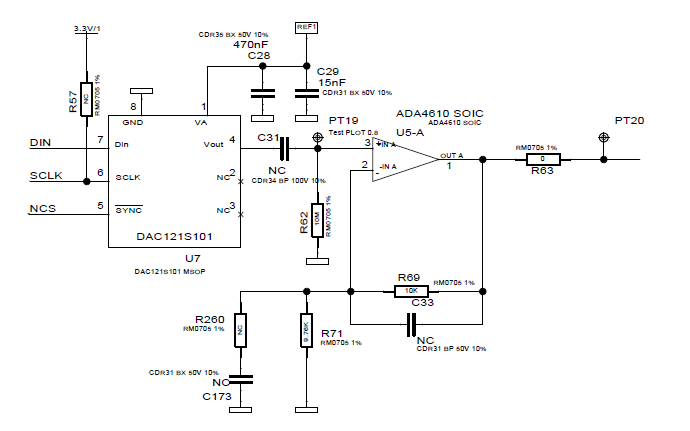

下面使用的电路。

输出是在 DAC 的引脚4处测量的、电容器 C31已组装且未组装、这两种情况下的行为没有变化。

如果有任何协助或指导,将不胜感激。

谢谢!