主题中讨论的其他器件: TSW14J10EVM、 LMK04828、

您好!

我正在对 ZCU106电路板+ TSW14J10 (修订版 C)+ ADC31JB68EVM (修订版 B)执行几乎相同的测试。

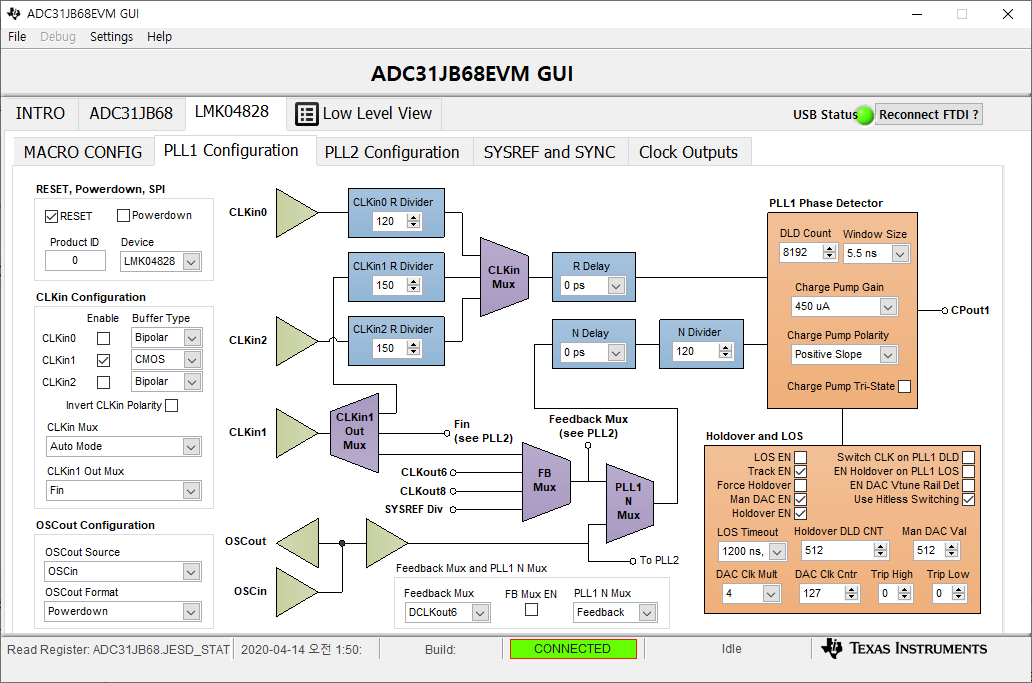

我将 Agilent N5181A 信号发生器的500MHz +12dBm 输出用于 CLK 输入。

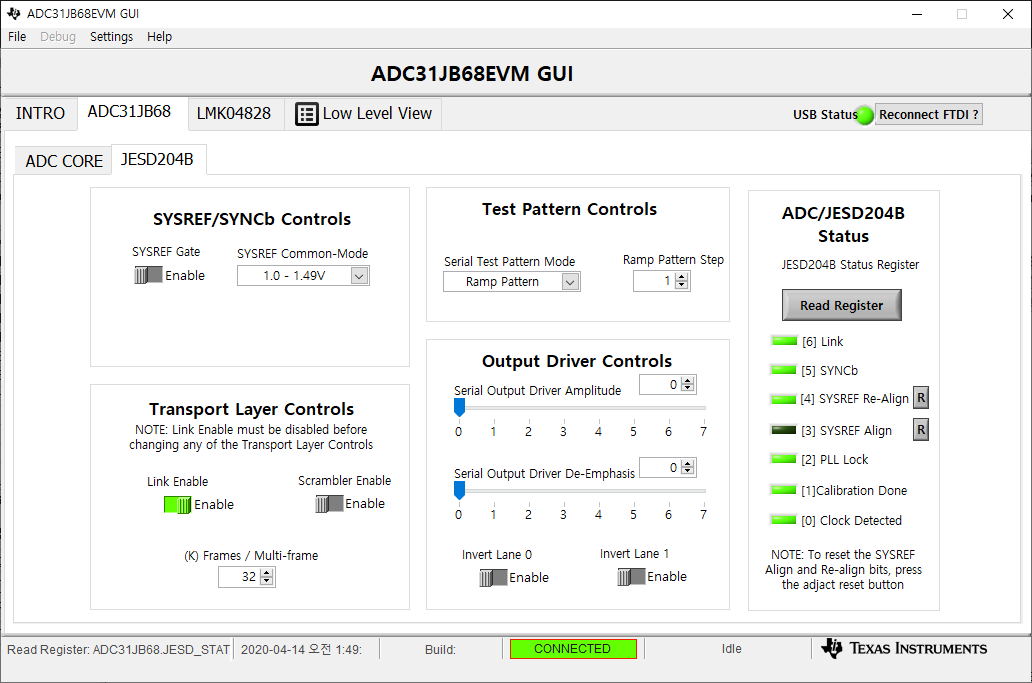

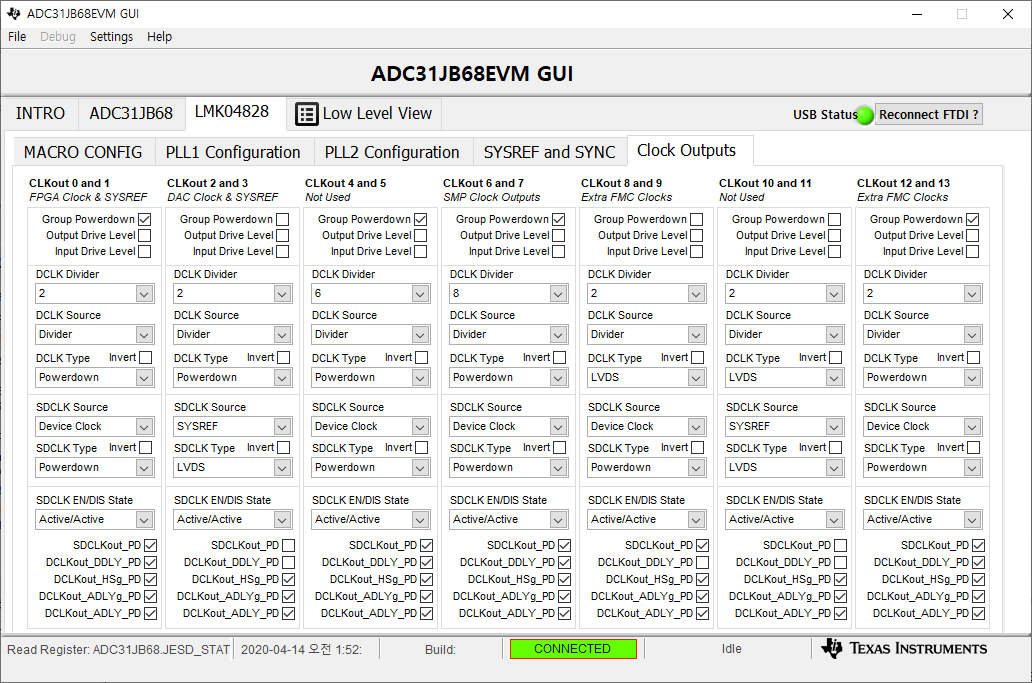

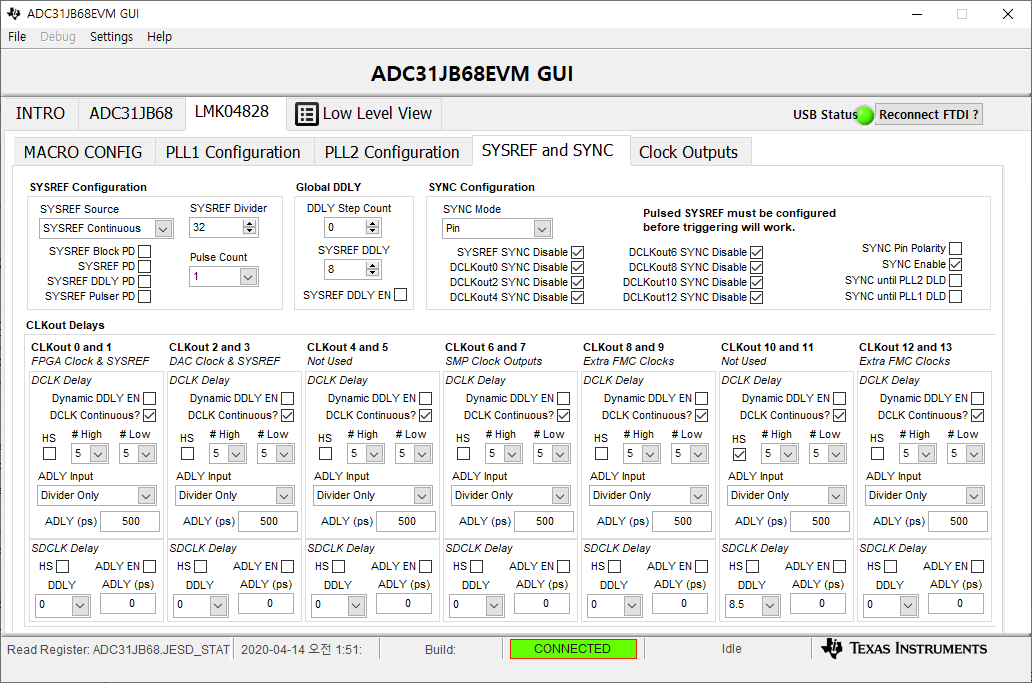

我已修改两个寄存器((R44-R45至 R51-R61)以使用 LMK_ADC_SYSREF (SDCLKout3)。

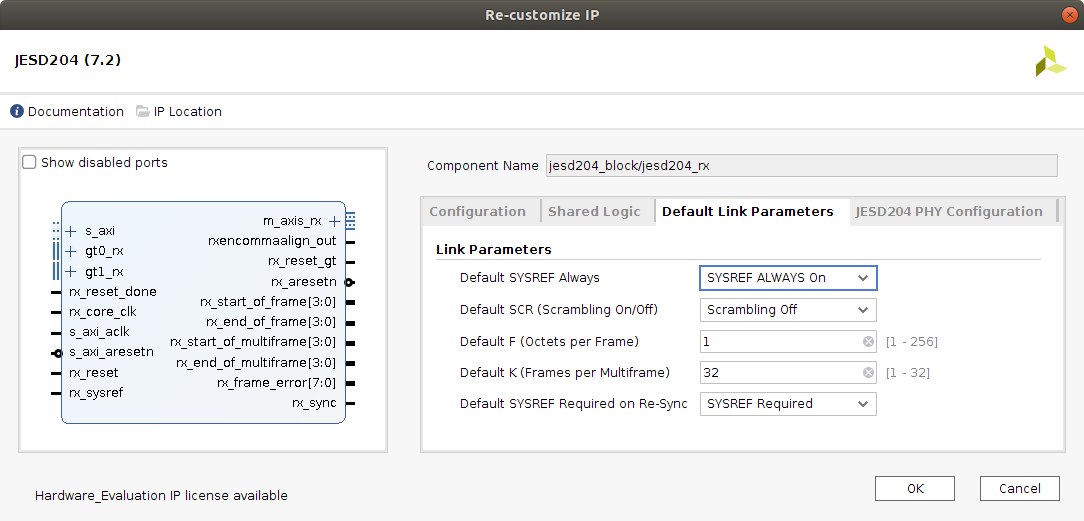

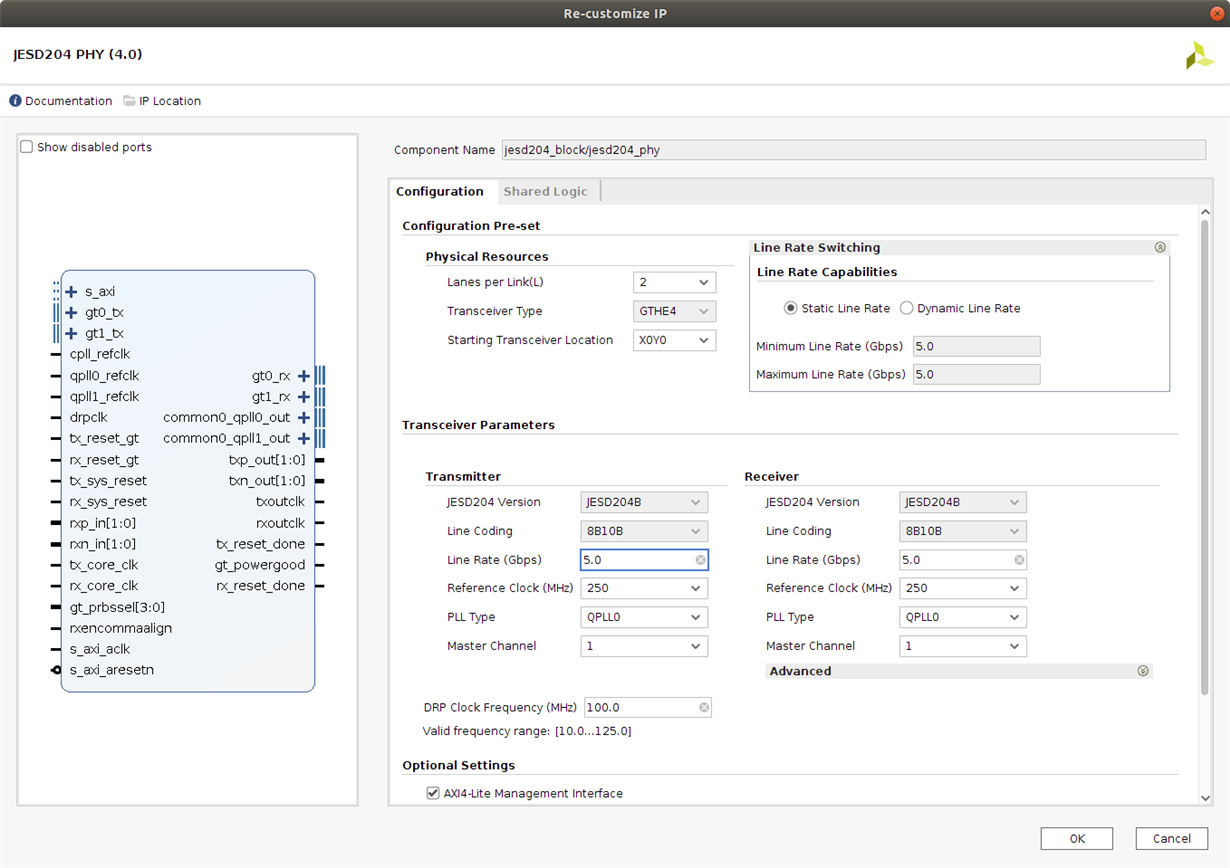

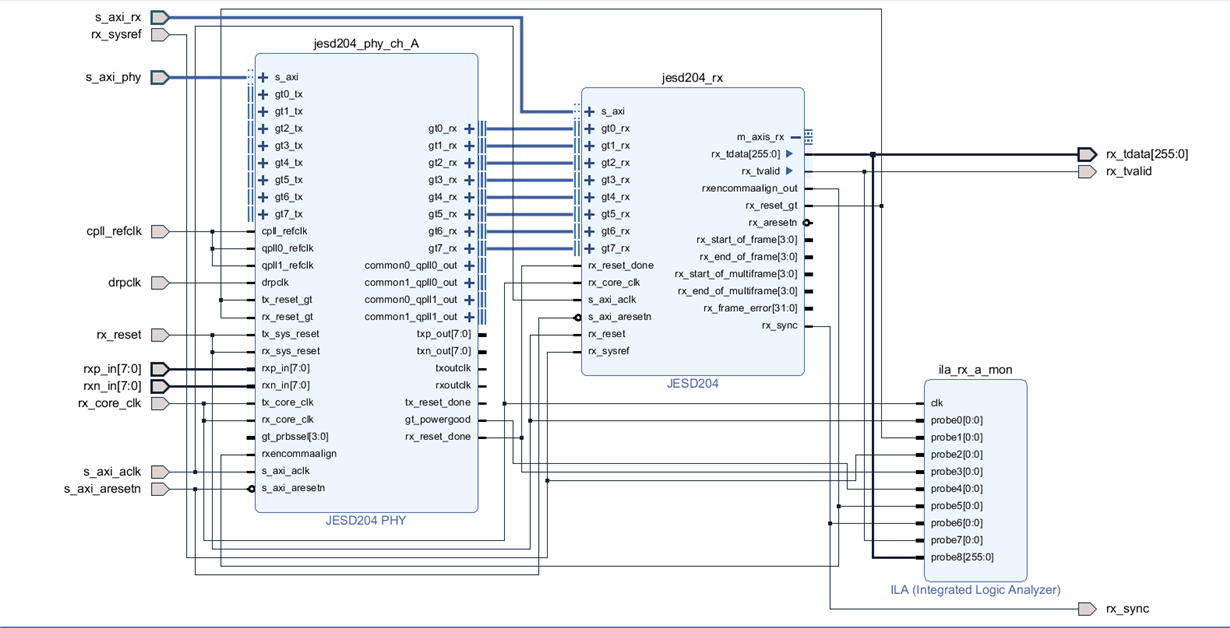

我还修改了 Vivado 2019.2和 Vitis 的设计和固件。

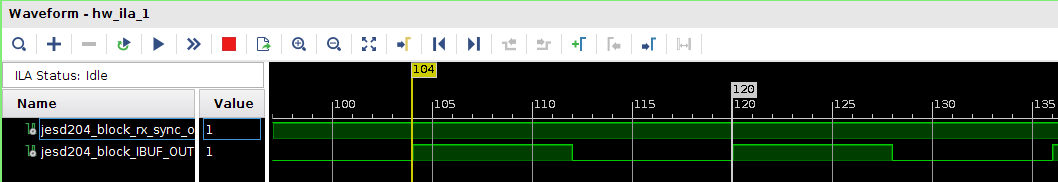

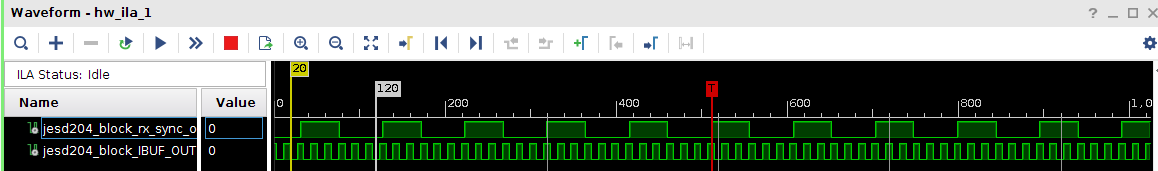

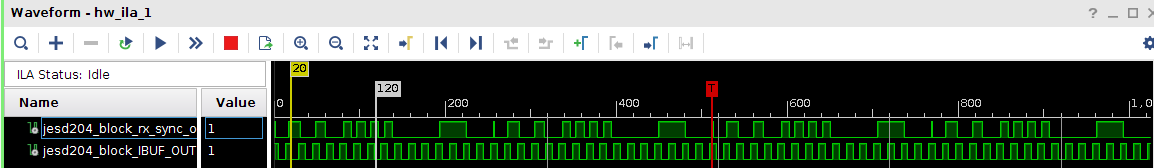

但是、链路非常不稳定且很难连接。

尝试数十个复位后、我可以链接 JESD204b。

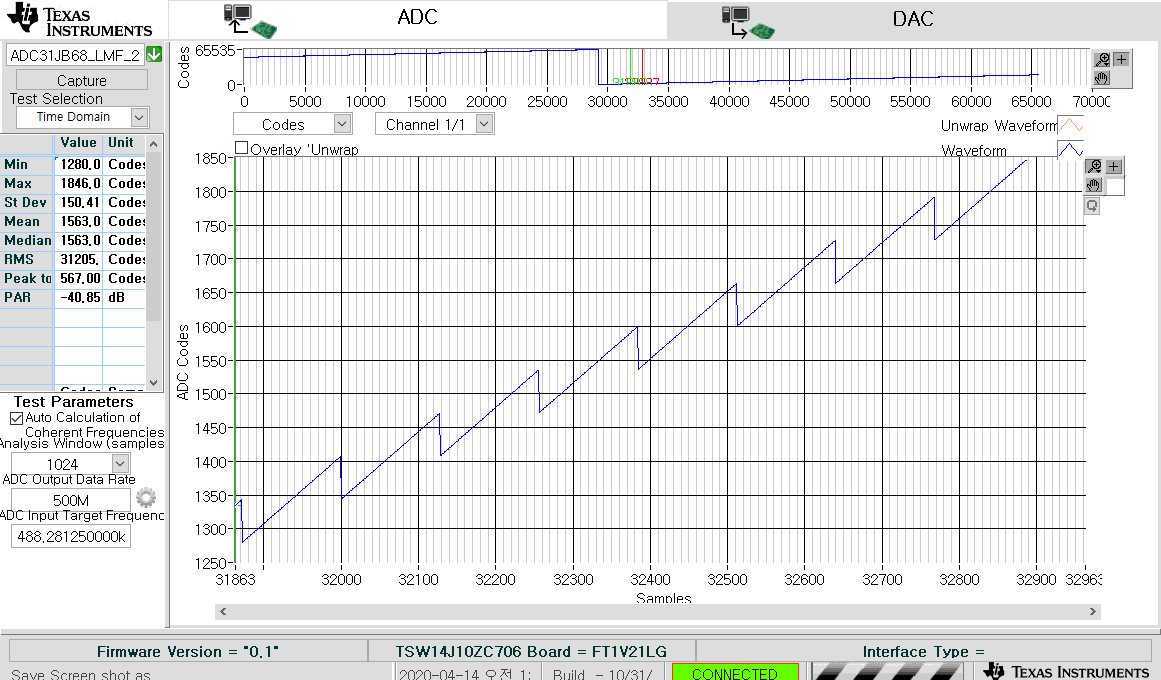

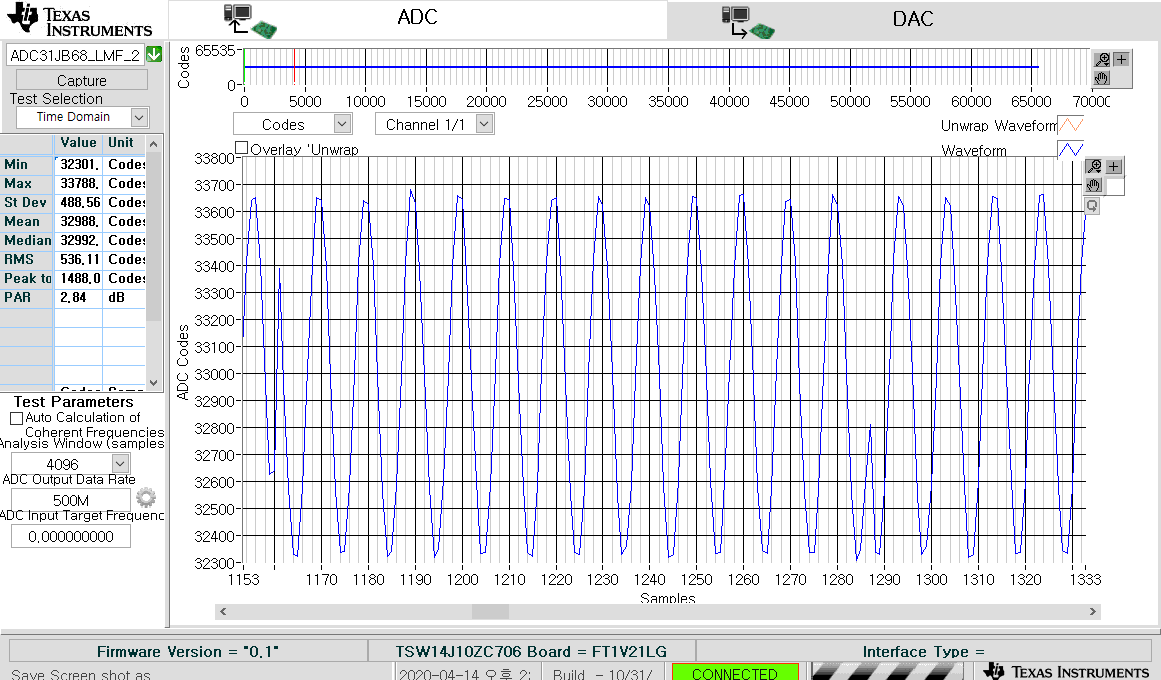

我的斜升模式下。 这是正确的模式吗?

我已将原始数据导出为 csv 文件并附加它。

每128个采样间隔。 减小为-63。

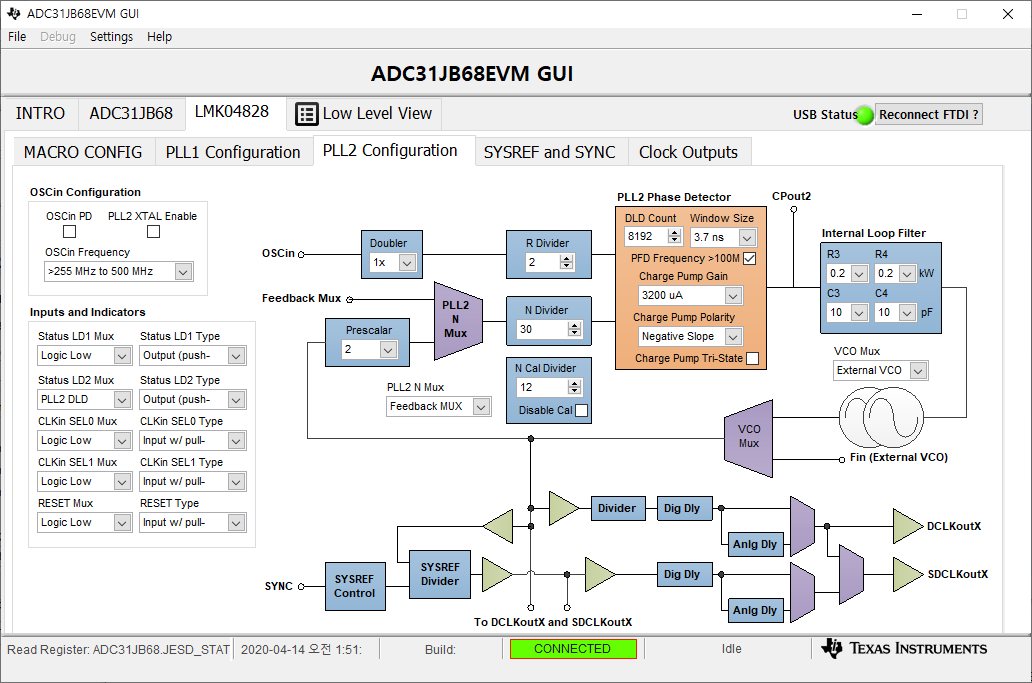

下面是 GUI 设置。