大家好、

我有两个问题。

------

[第1季度]

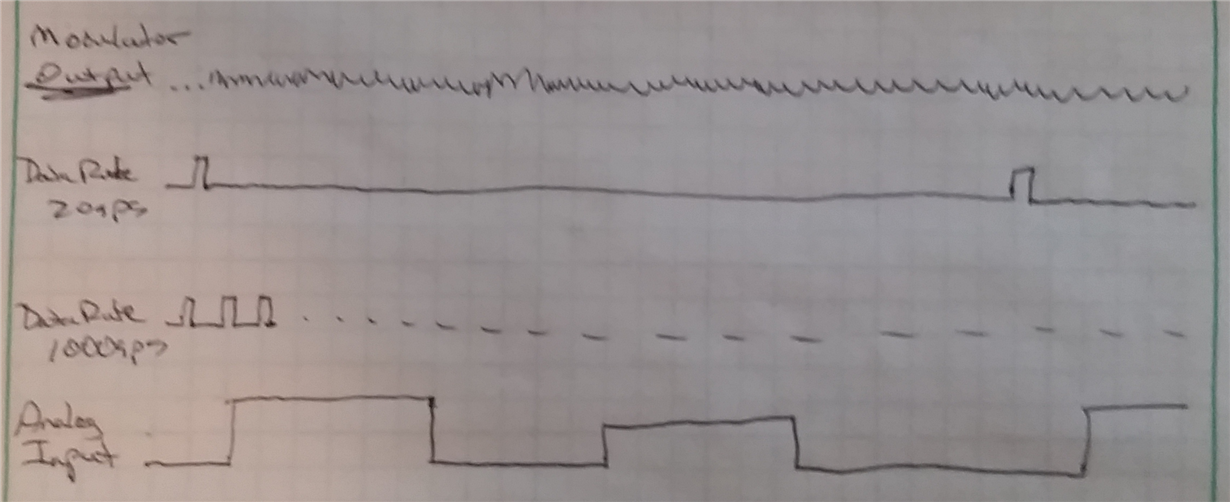

我们使用两个差分信号(AIN0和 AIN1对、AIN2和 AIN3对)。

然后、我们想知道以下稳定时间。

我的猜测序列

AIN0和 AIN1对开启、AIN2和 AIN3对关闭

更改差分信号

AIN0和 AIN1对关闭、AIN2和 AIN3对打开

4.要达到稳定时间?uS (我们必须等待超过?uS)

5.AIN2和 AIN3对数据可用于 AD 转换

------

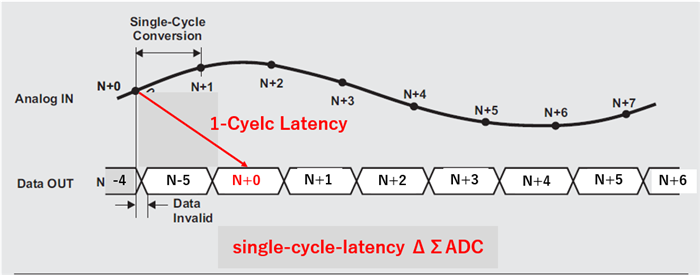

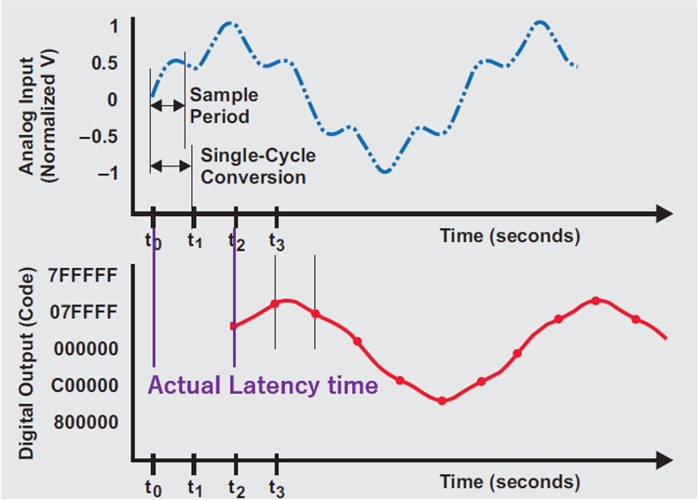

[第2季度]

我们想知道延迟(从输入模拟日期到输出数字数据的等待时间)。

如果您有任何信息、请告诉我们吗?

------

此致、

隐藏