主题中讨论的其他器件:ADS54J66EVM、 ADS54J66、 DAC37J82、 LMK04828、 DAC5675A、 DAC38J82

设置- ZCU102连接到 HPC1上的 ADS54J66EVM 和 HPC0上的 DAC37J82EVM。

ADS54J66参数- LMFS = 4421、K = 32、307.2MSPS、线路速率= 6.144Gbps、Sysref = 2.4MHz、模式8 (旁路 DDC)、VCO 0 = 2457.6MHz

输入频率-所有4个 ADC 通道上为70MHz

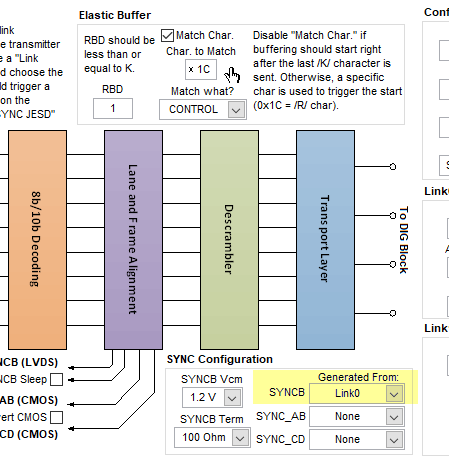

FPGA RX JESD - 4通道、REFCLK = 153.6MHz、Coreclk = 153.6MHz、CPLL、线路速率= 6.144Gbps

FPGA TX JESD - 8通道、REFCLK = 153.6MHz、Coreclk = 153.6MHz、CPLL、线路速率= 6.144Gbps

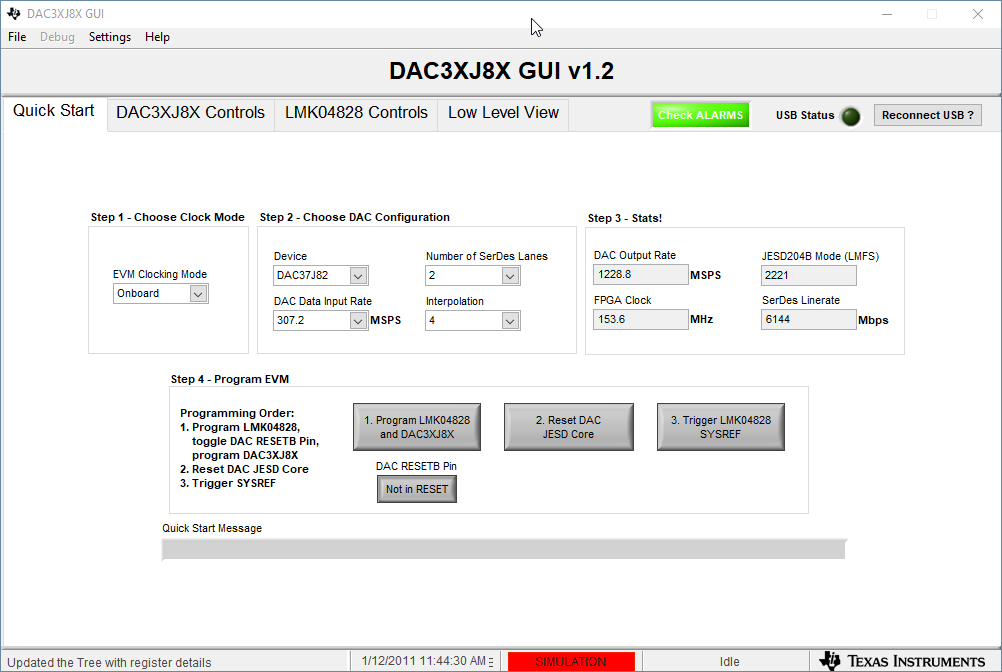

DAC37J82参数-?

我希望设置一个回送、在该回送中、来自 ADS54J66的4个通道的传入实例数据将被发送到 DAC37J82的1、2或全部4个通道。 发送到 DAC 的实际采样数据不一定是所有4个通道的数据。 它只能用于1个通道(A、B、C 或 D)。 例如、ADC 通道 A 至 DAC 通道 A

我将进行此设置、以测试 FPGA、ADC 和 DAC 之间的 JESD 接口、并熟悉数据转换器。

我在 JESD RX 和 TX 模块之间使用128 in、256 out FIFO。 我只为8个通道设置了 FPGA JESD TX 模块、因为 DAC37J82有8个通道、但如果使用的通道较少(LMF 222或421)、则256位 AXI 流总线上的其余位将设置为零。

请确认此设置并建议 DAC37J82的配置。 我是否必须将 DAC 和 ADC EVM 上的 LMK04828芯片与外部参考时钟同步? 谢谢你