主题中讨论的其他器件: LMH6401

你(们)好

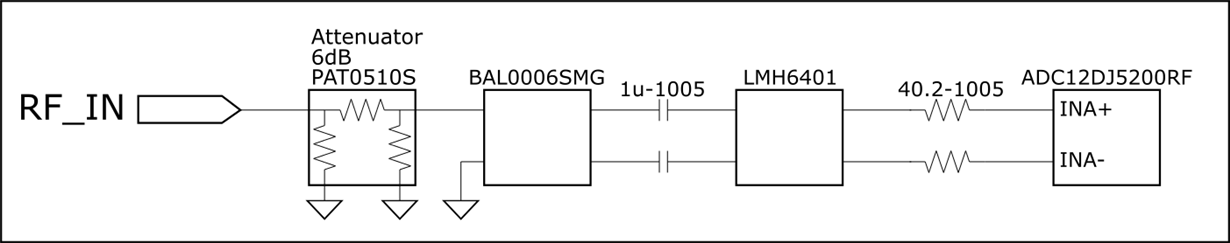

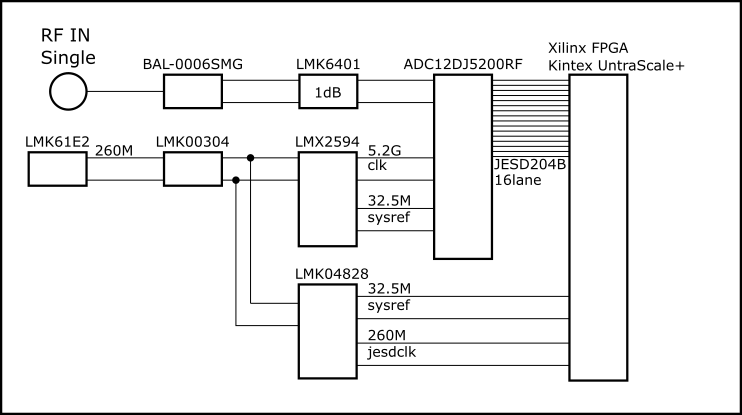

我在自己设计的电路板上使用 ADC12DJ5200RF。

目前,我所面对的问题是,广告转换的结果有时会受到干扰。

当我在问题发生时读取 ADC 寄存器时、地址0x2B2的[7:0]值与正常操作不同。

因此、我想问、当前初始启动过程是否有任何问题。

・为 FPGA 和 ADC 配置时钟和周期性 SYSREF

・设置 ADC 中的寄存器并执行 SYSREF 校准

・在 FPGA 中配置 JESD204 IP

・执行 ADC 的前台校准

FPGA 中的・μ s SYSREF 延迟调节

ADC 和 FPGA 以 JESD204B 的子类1进行连接、SYNC 信号表示连接有效。

但是、有时 AD 转换的结果会变得非常嘈杂、以至于无法看到波形。

这种情况是否有任何出路?

我按照第9.3节中的设置 ADC 寄存器的过程进行操作。