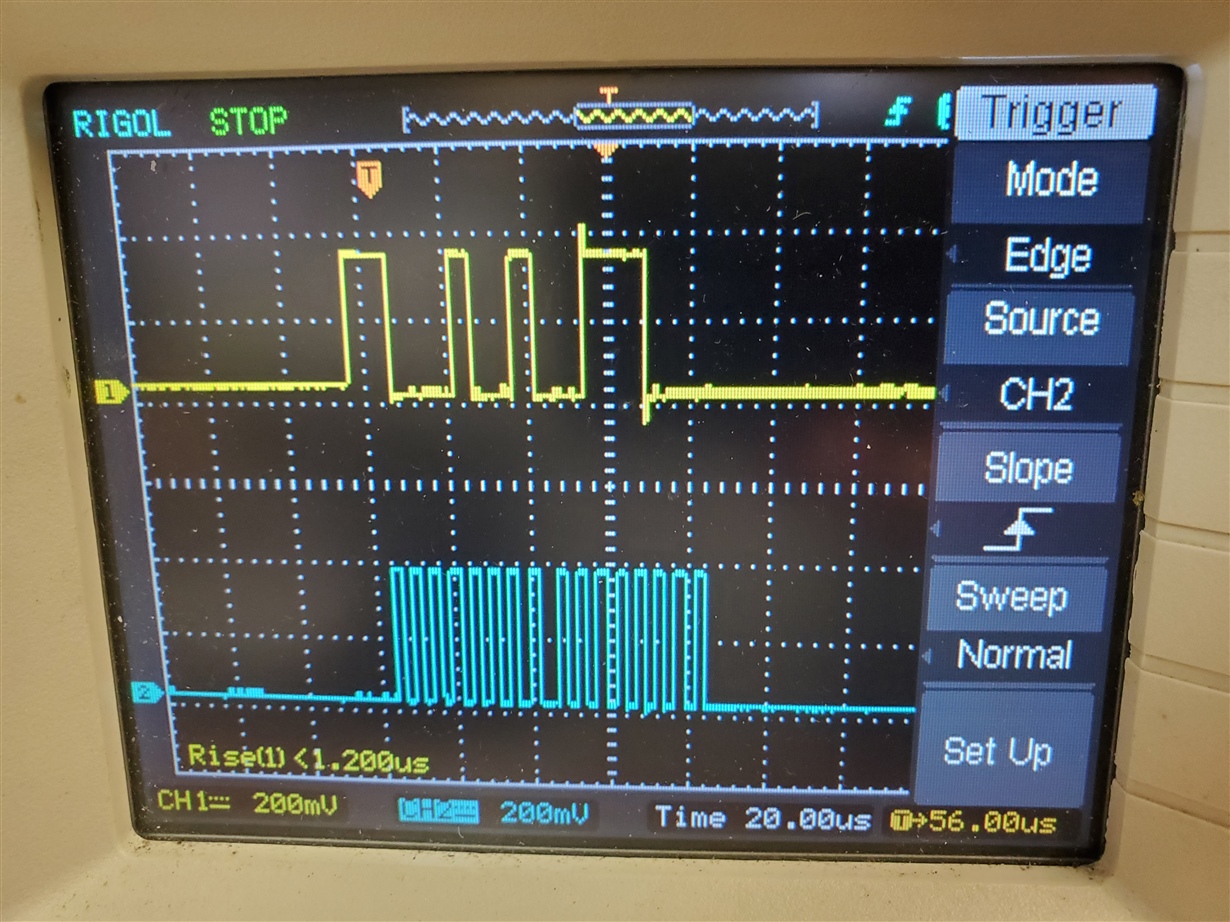

我一直在项目中使用 ads8866、在 perf 板上制作初始原型、效果良好(也可以预期在电线悬空的情况下)。 一切看起来都正常、所以我将其移到了 PC 板上。 现在、使用相同的软件(引脚分配、时序和一切)、我最初焊接在 ADC 上、但它根本不起作用。 在示波器上、DOUT 引脚启动3V 并立即降至零、并保持在该状态。 我想在安装时它可能已损坏、因为我用手焊接了它。 把旧的那个取下、再把它放在一个新的那个上面、再仔细一点、这次又得到了一些数据。 然而、在仔细检查后、我意识到3个最低有效位始终为0。 其余的位似乎随着负载的增加而翻转、而不是最后的3个位。

这是由于焊接技术不良造成的、还是存在其他可能导致丢失位的问题? 这些东西在焊接烙铁的热量中有多脆弱? 我们是否应该尝试手工焊接这些?