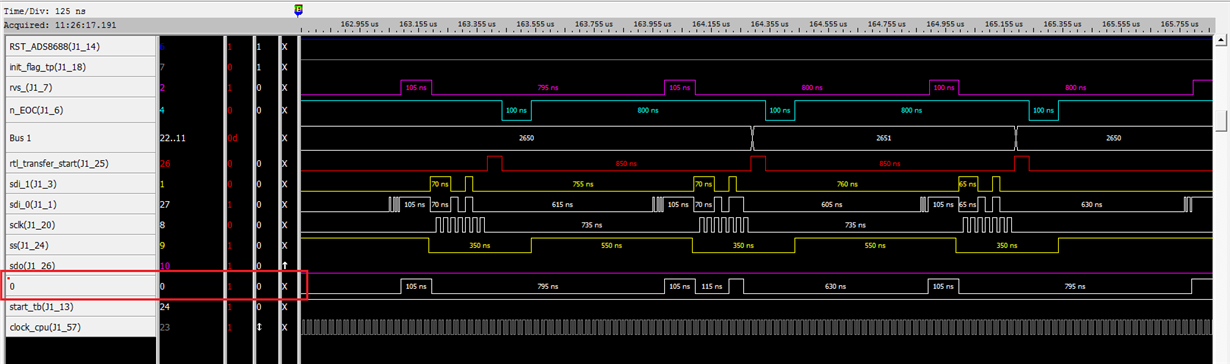

全部使用 CPHA = 0、CPOL = 0。

问题在于数据表的说明。

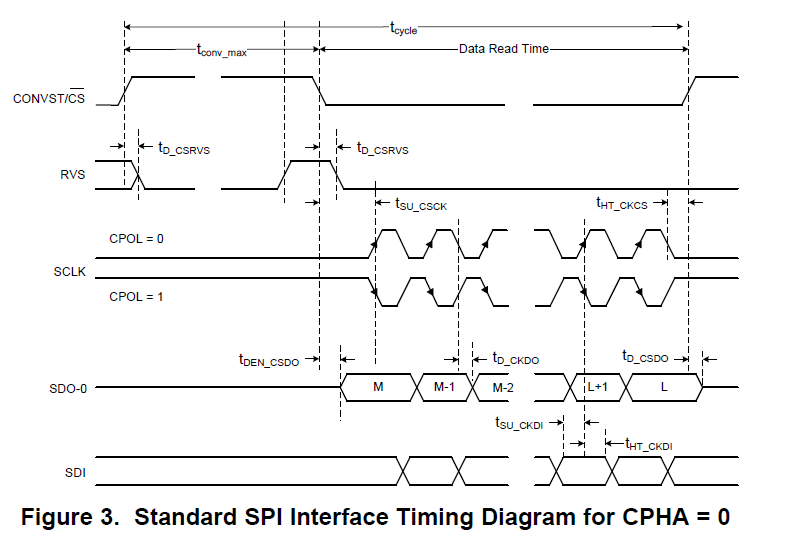

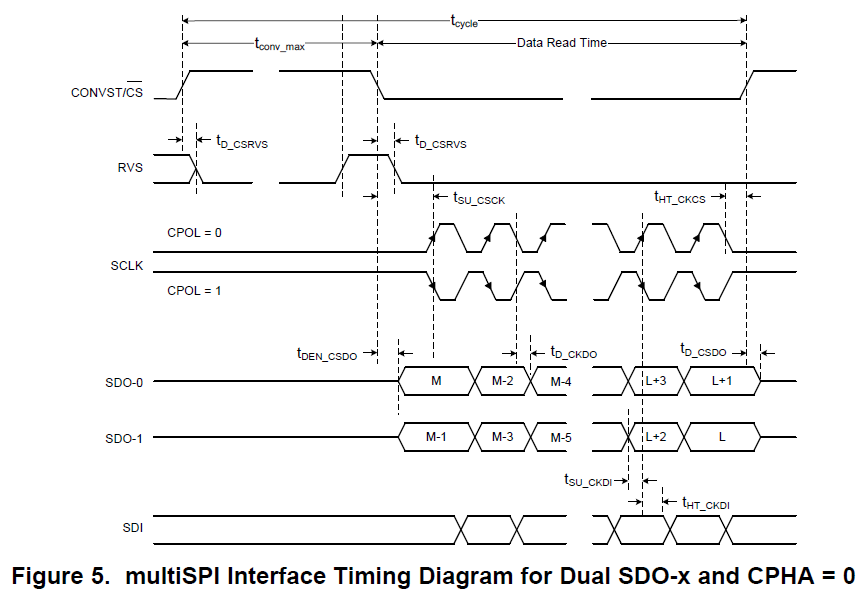

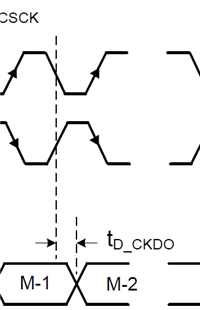

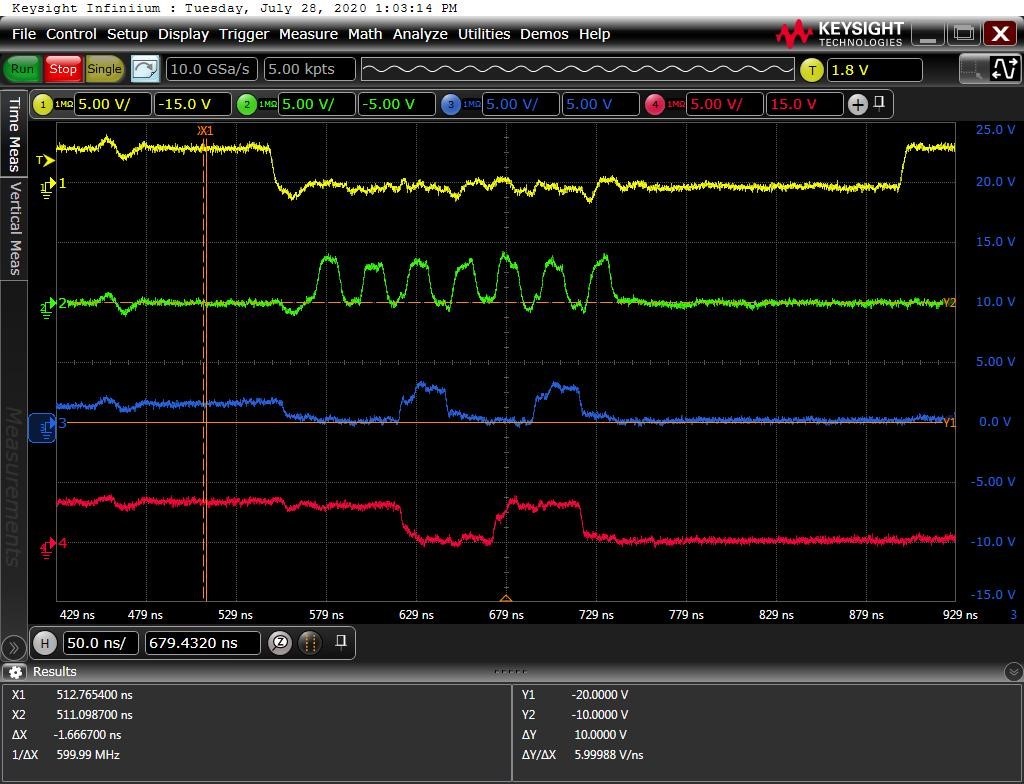

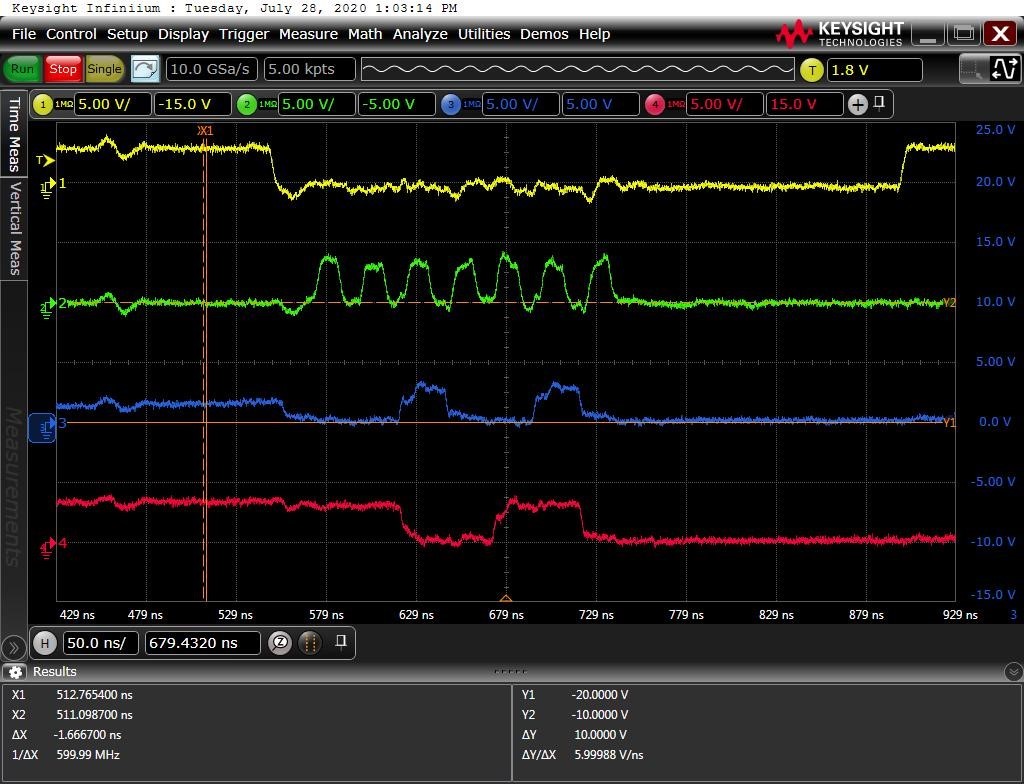

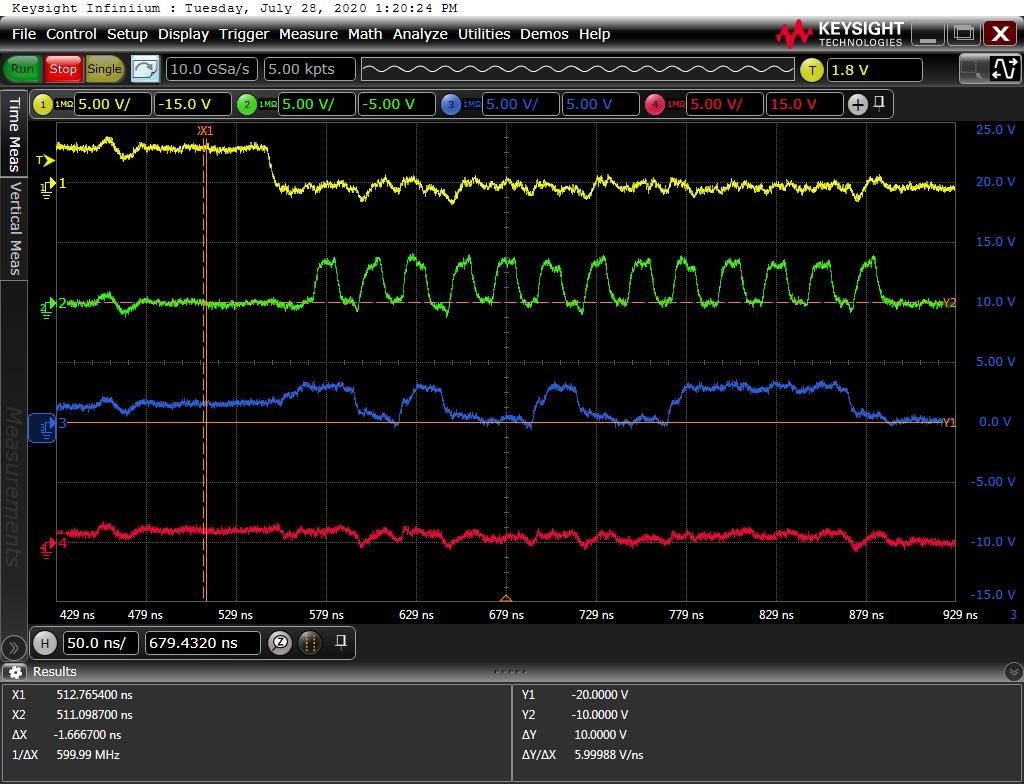

数据表显示,延迟时间,td_CKDO 为12ns,即 SCLK 启动边沿到(下一个) SDO-x 上有效的数据

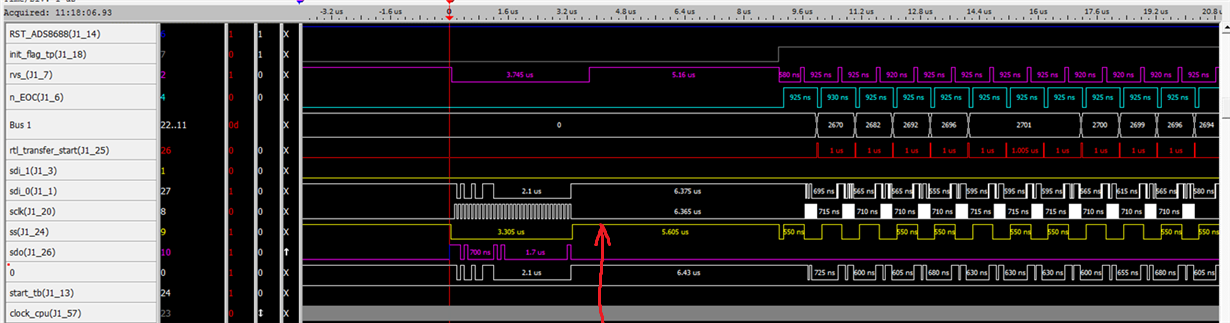

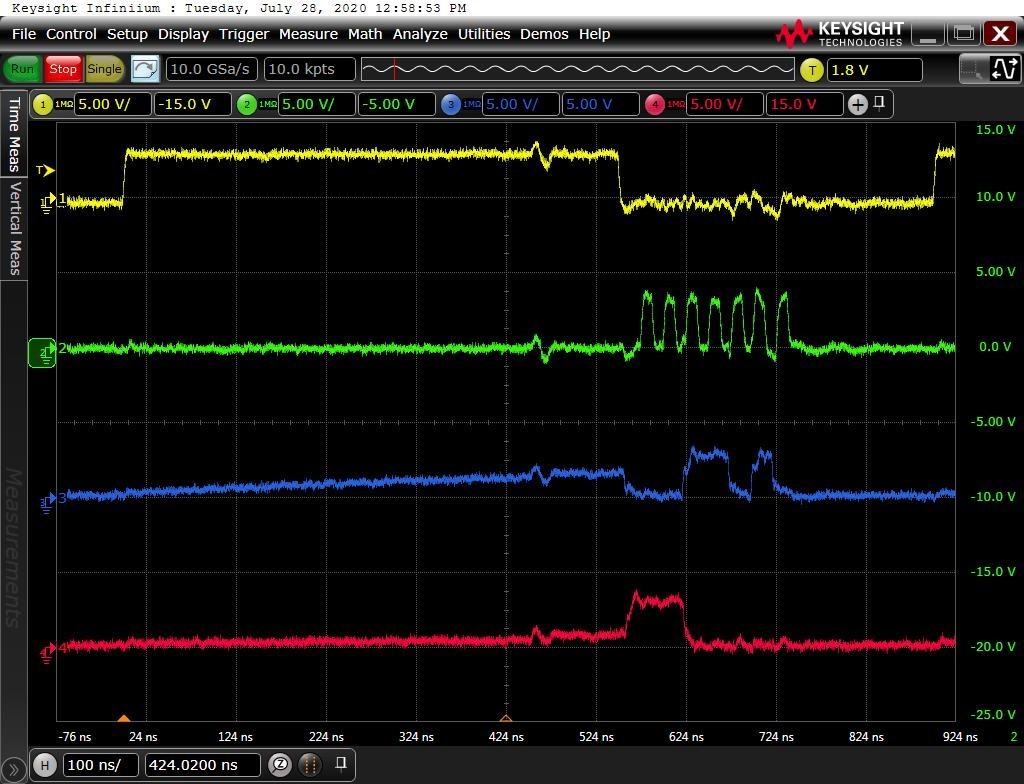

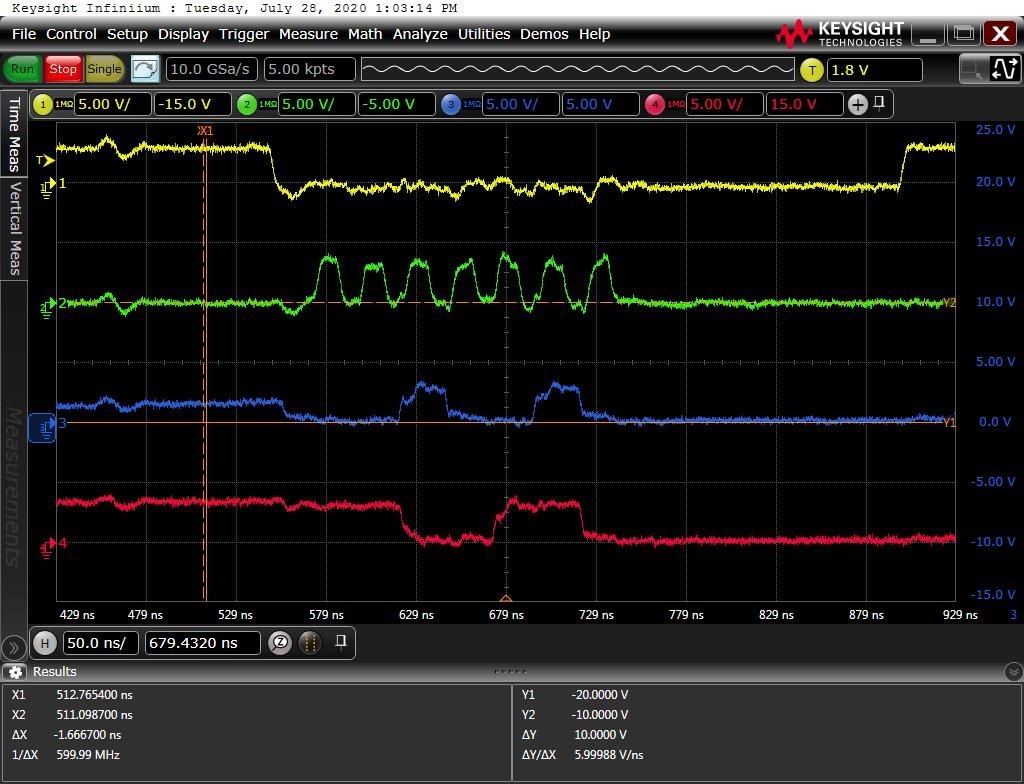

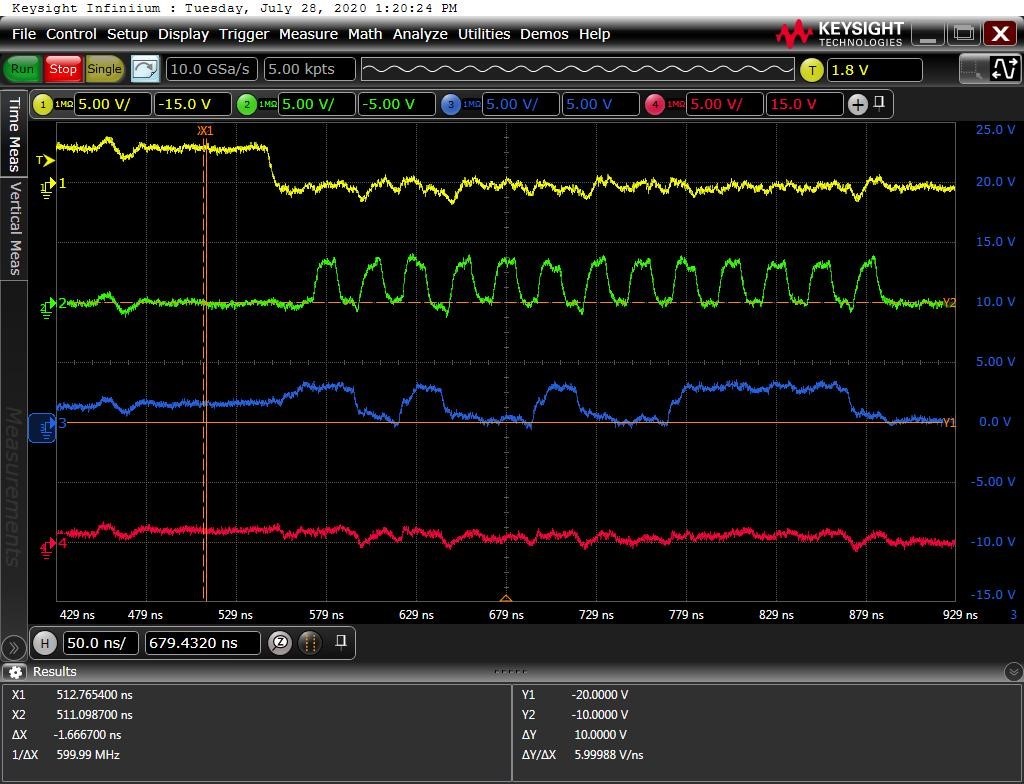

数据表中描述的显示、设置 CPHA=0、CPOL=0、CLK 启动边沿是上升边沿、但数据表中的图片为什么显示 CLK 是下降边沿?

相反,数据表中描述的是,设置 CPHA=0,CPOL=1,SCLK 启动边沿是下降边沿,但为什么数据表中的图片显示 CLK 是上升边沿?

问题是哪种描述是正确的、图片或文档叙述?

2.

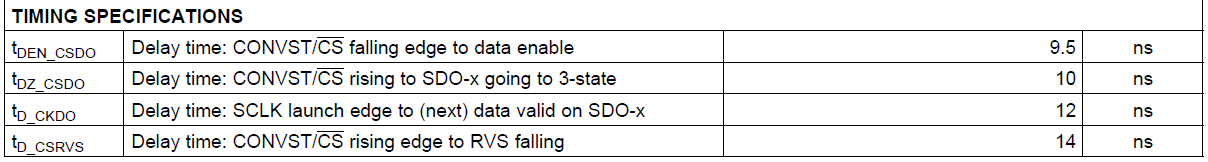

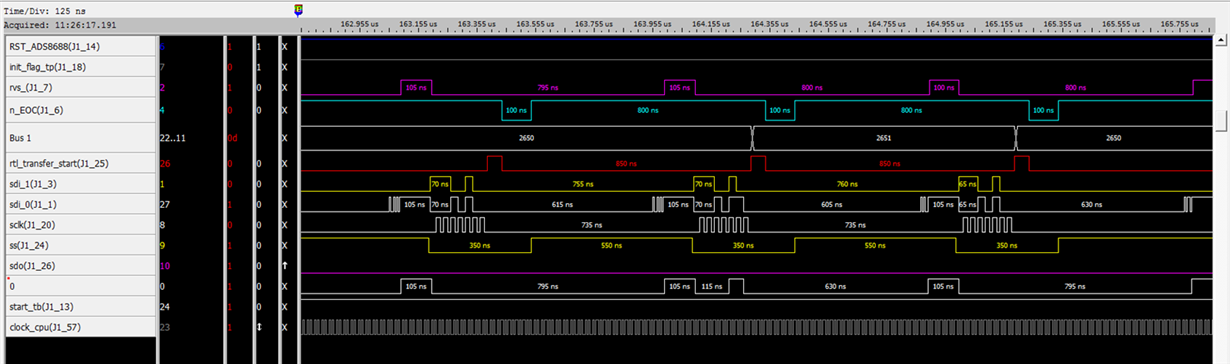

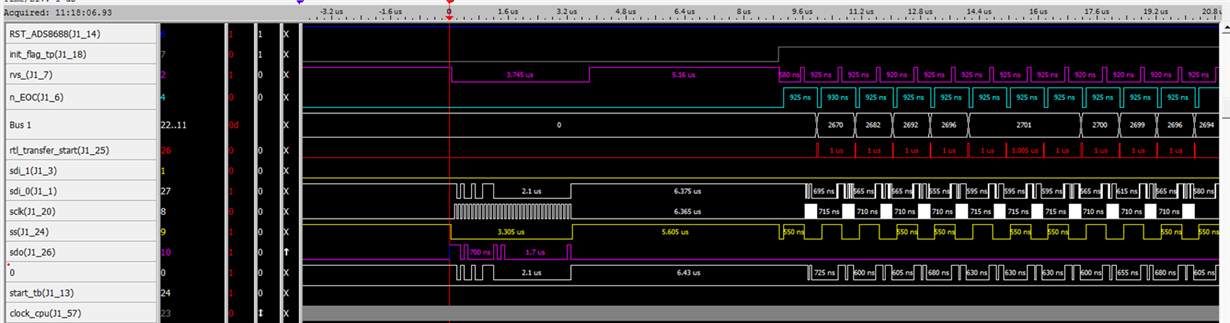

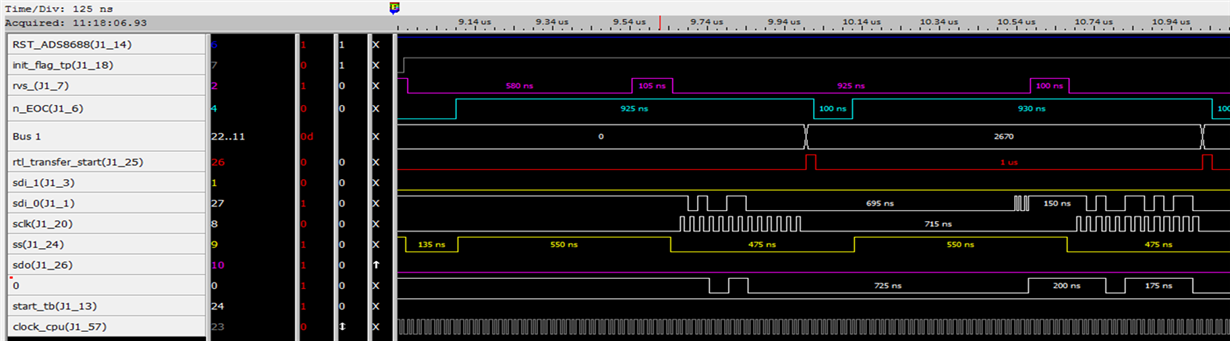

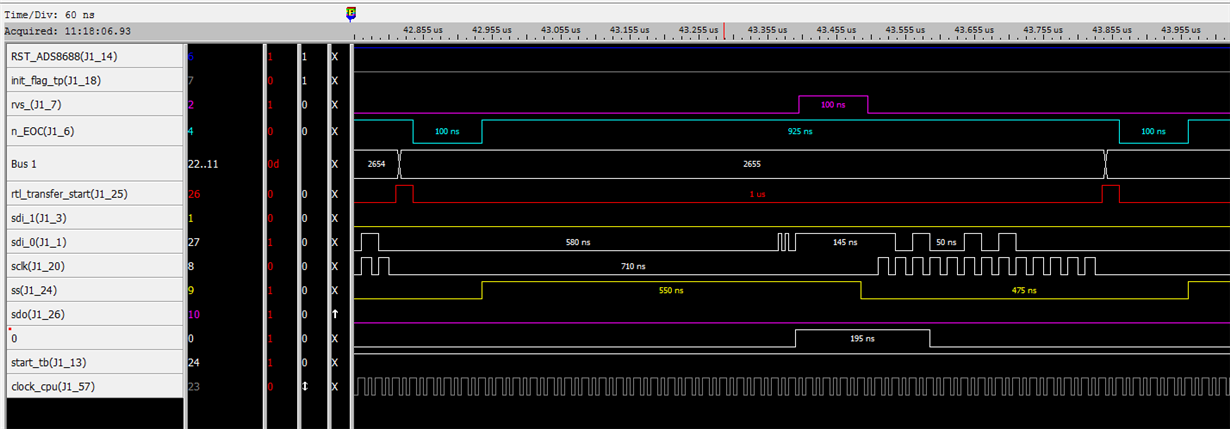

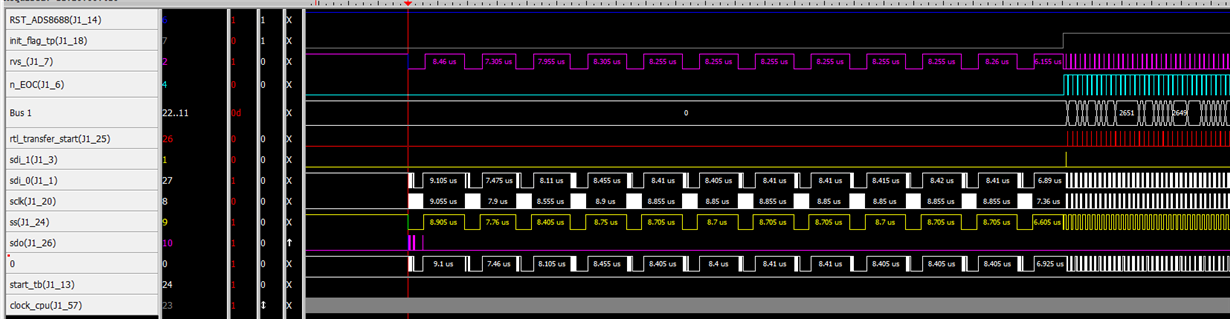

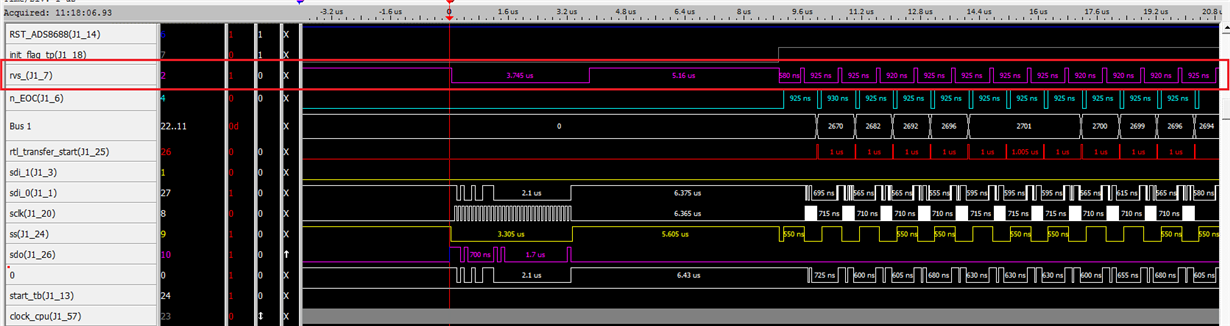

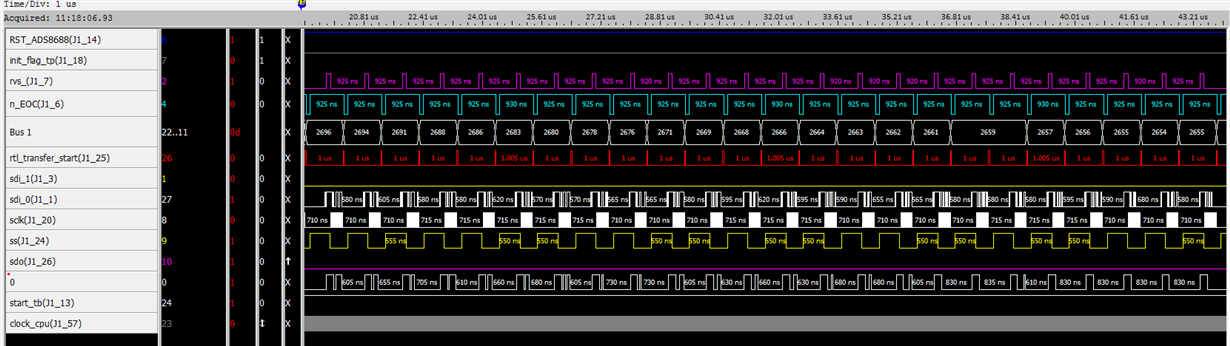

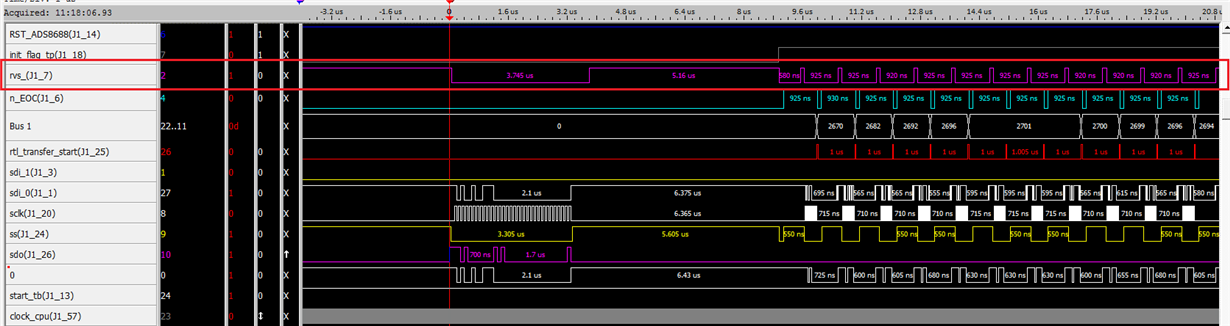

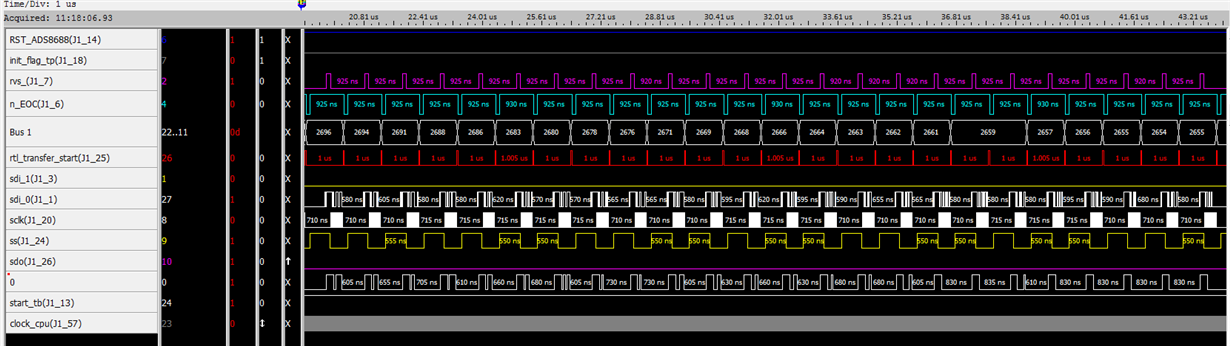

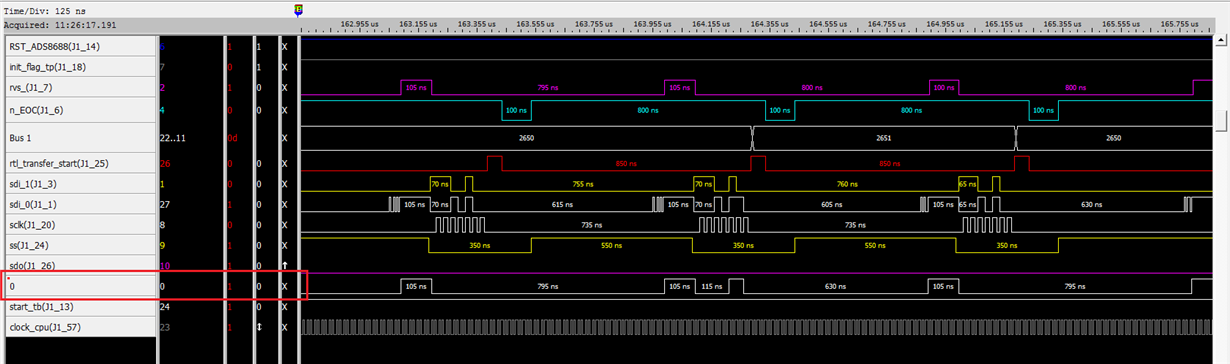

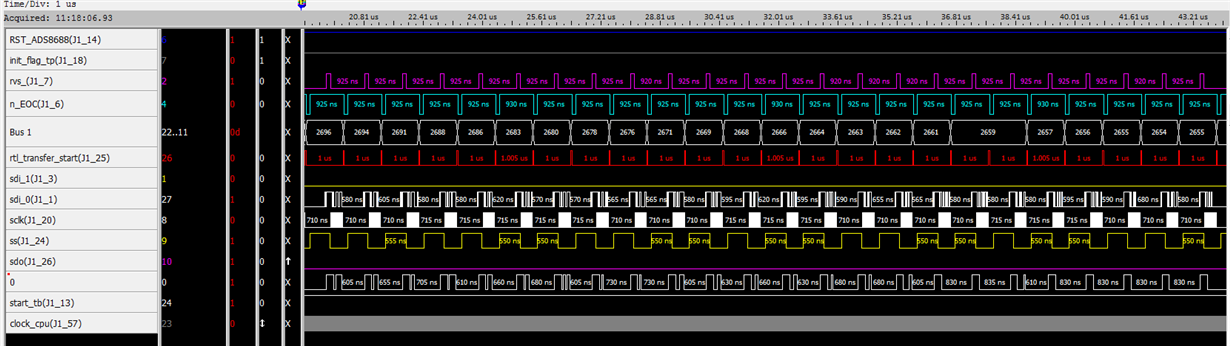

在双 SDO 模式下,数据表显示 SDO-0传递到 MSB,然后 SDO-1传递到 MSB-1……,然后继续。 但实际测试结果恰恰相反。

是疏忽控制、还是芯片动作与描述不同?

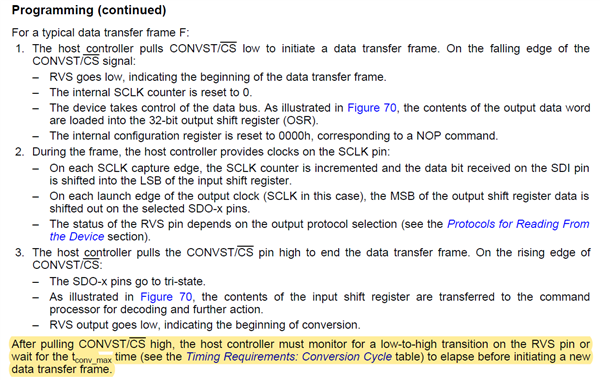

3.编程:

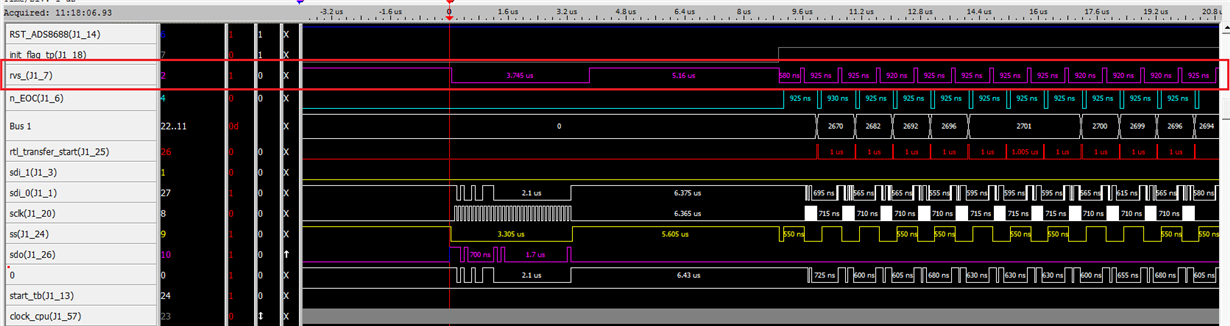

我设置了 Vref x+/-2.5 (即符合时间规则),在重复读取转换时间数据大约4~5次之前无法获得正确的数据。

是否有人发生过这种情况、以及如何解决?

谢谢。