Other Parts Discussed in Thread: DAC5672

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC5672 大家好、我在我的定制板中使用 DAC5672器件、从 Xilinx Artix-7 FPGA 向 DAC 提供数字数据输入。

- 14位正弦波数字数据从 FPGA 馈送到 DAC。

- DAC 在双总线模式下使用、仅使用通道 A。

- DAC 的输入数据速率为40MSPS;每正弦波16个点;正弦波的模拟频率为2.5MHz。

- DAC 采样时钟频率为80MHz、仅由 FPGA 提供。

- "时钟"和"写入_enable"信号是相同的连续自由运行时钟。

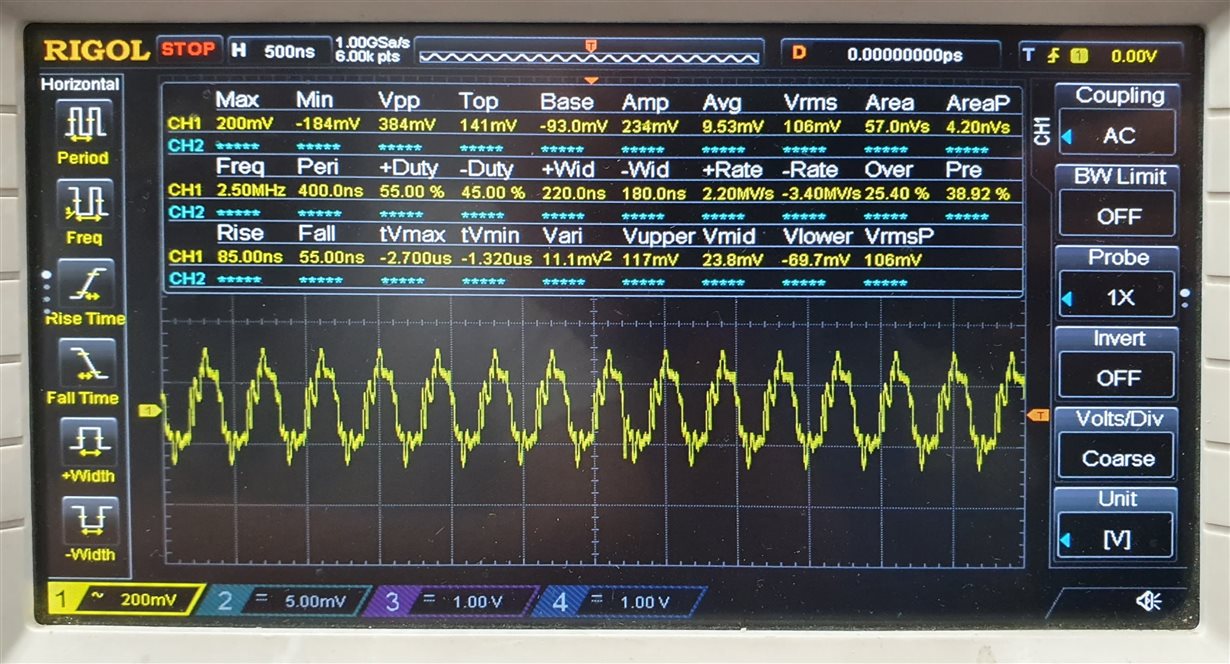

DAC 的模拟输出存在噪声、有毛刺脉冲。 随附了相同的示波器快照以供参考。

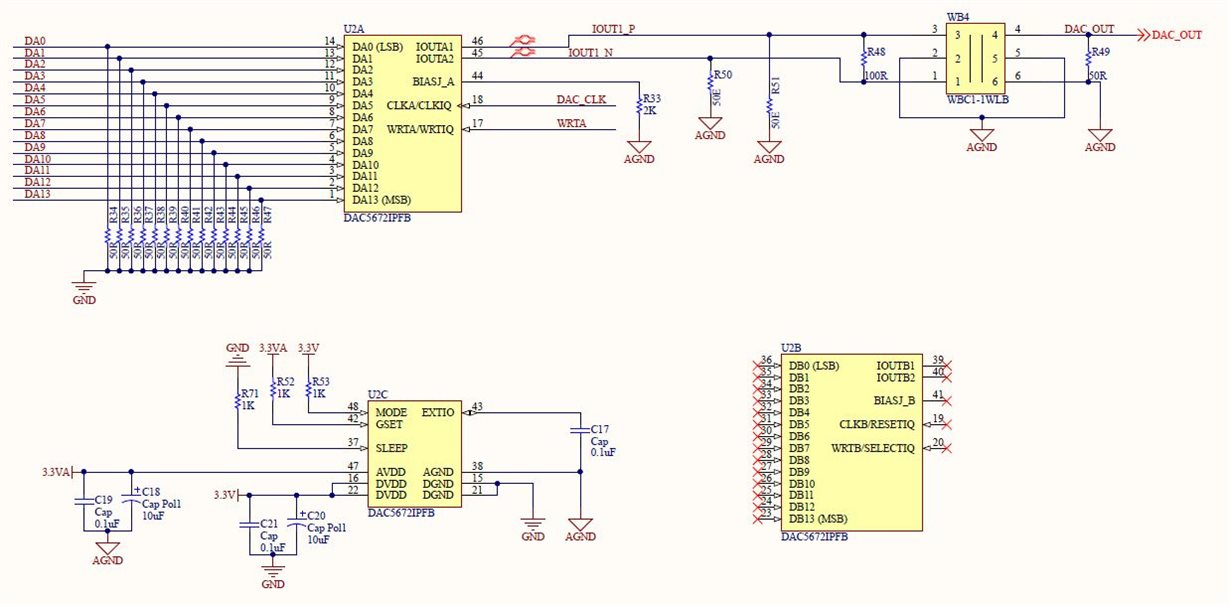

此外、还随附了 DAC 的原理图以供参考。

参考下面的原理图,输入位 DA0...... 原理图中的 DA13、WRTA、DAC_CLK 直接从 FPGA 路由。 变压器输入端的100欧姆"R48"电阻器被省略。 DAC 的输出在 "DAC_OUT"网络中探测、该网络是1:1变压器的输出。

需要有关调试和解决问题的帮助。

谢谢。