主题中讨论的其他器件:DAC3482、 CDCE62005

对于 DAC3482EVM、提供了一个寄存器配置文件作为 参考: "DAC3482_FDAC_1228p8MHz_4xint_NCO_30MHz_QMCon.txt"

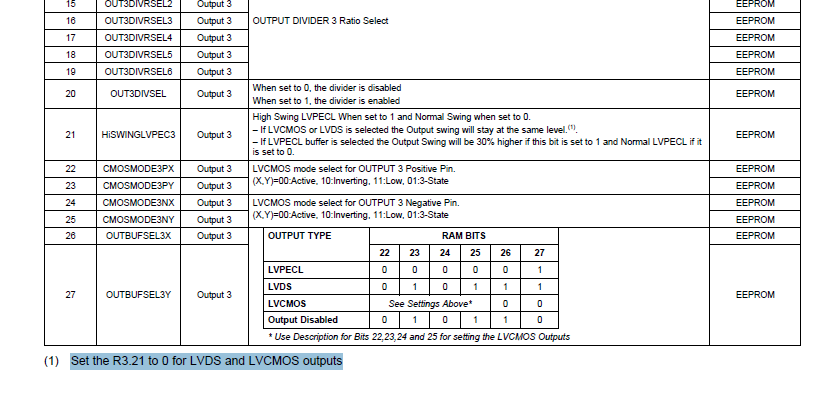

这将配置 DAC3482和 CDCE62005寄存器。 该 文件中的寄存器 CDCE62005 x3条目定义为"C10C0003"。 当我查看 该寄存器的 CDCE62005手册时、指定的位设置与该手册不一致。 以下是 CDCE62005手册中的相关手册页面:

值0xC10C0003转换为(对于这些位子集)

位21 = 0

位22 = 0

位23 = 0

位24 = 0

位25 = 0

位26 = 1

位27 = 1

从 CDCE62005手册中不清楚配置文件尝试实现的目标。 该位映射似乎不是有效的组合。 我认为这很重要、因为这个时钟驱动 FPGA 时钟引脚、所以我猜它很重要。