主题中讨论的其他器件: ADC12D1000

尊敬的 TI 专家:

我对 ADC10D1000有一些技术问题、如下所示。

我 看到 Vcmo 被内部缓冲。 TI 是否建议将该引脚直接连接到全差分放大器(FDA)的共模输入引脚、或在将其连接到 FDA 之前对其进行外部缓冲?

2. 如果不使用 TDIO2+-引脚、是否可以将其保持悬空(未连接)?

在 数据表中显示的典型性能图中、使用了多少个样本来执行 FFT?

CalDly 的等效电路显示它是 CMOS 输入引脚。 为什么推荐的上拉/下拉电阻器为1k Ω? 注意事项是什么?

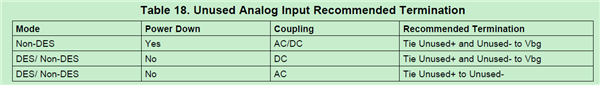

5、 如果 ADC 以 Desi 模式和1:4多路信号分离器模式运行、能否使用 DCLKI 锁存 DQ 和 DQd 并保持 DCLKQ 悬空(因为 DCLKI 和 DCLKQ 始终同相)、或使用100 Ω 电阻端接 DCLKQ、但不将 DCLKQ 连接到 FPGA? 如果 ORI 为高电平表示 Vini 超出范围、如何确定哪个样本超出范围、因为目前 DI 和 DID 都计时输出? ORQ 是否在1:4多路信号分离器模式下有效?

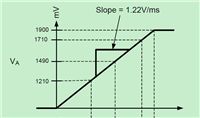

6. 该部件是否需要特定的电源斜升速率?

7. 对于 DES 模式中未使用的交流耦合输入、建议采用哪种端接方法? 表18说明应该将未使用+连接到未使用-、而数据表(交流耦合输入信号部分、第60页)也提到未使用的交流耦合输入应该通过电容器接地。

8. 在 DES 和非 DES 模式下、未使用的直流耦合输入应连接到 VBG、对吧? 我们应该如何连接它们是否有任何要求? 例如、我们应该通过具有特定特性阻抗的布线或低阻抗平面将它们连接起来吗?

9. 如何在非 ECM 模式下终止未使用的 SPI 引脚?

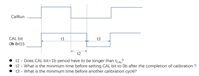

10. 校准的时序要求是什么,如下所示?

期待您的回复。 谢谢。