主题中讨论的其他器件: THS4511、 ADS54J60

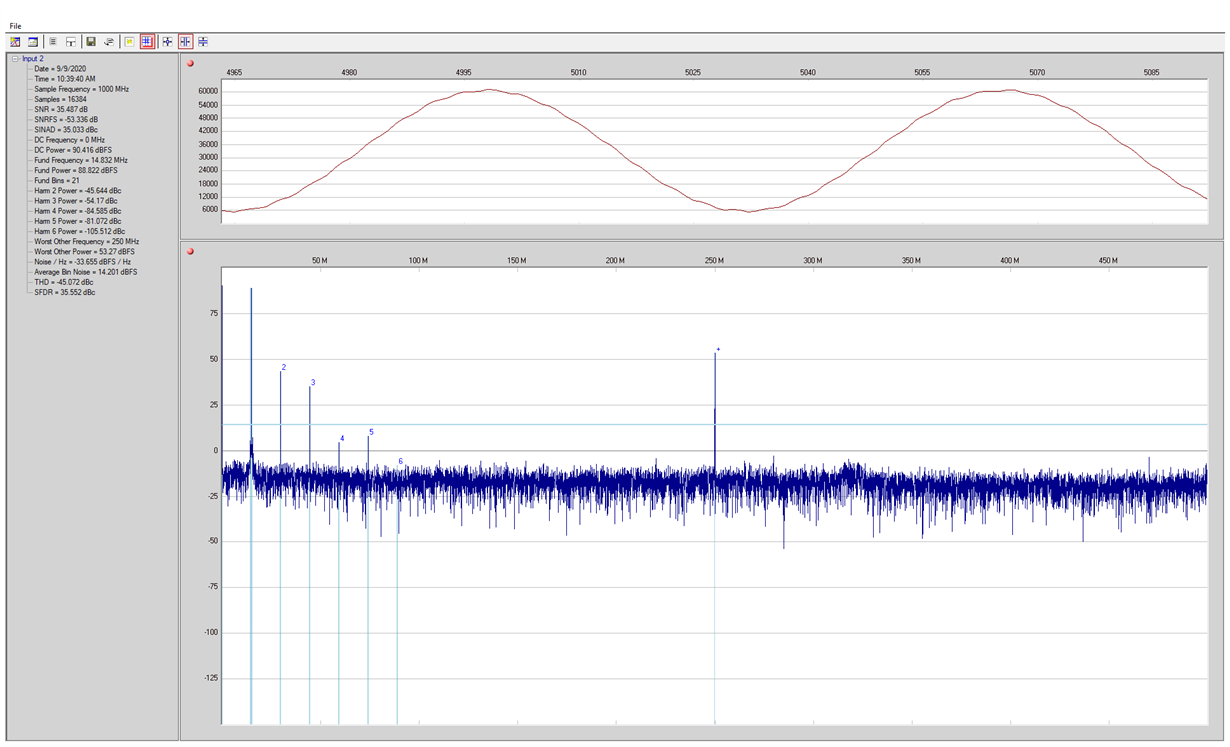

大家好、我有一个具有 ADS54J40的原型板、它通过 FMC+连接器使用8条通道连接到 FPGA。 遗憾的是、其中一个通道连接到错误的 FMC+引脚、因此我在4通道模式下使用 ADC。 JESD 正常工作、我可以接收正确的数据、但信号频谱始终为250MHz (即使是未连接的输入)、这是采样频率1GHz 的四分之一。 我们尝试将其更改为900MHz、从而产生225MHz 的寄生频率(同样是采样频率的四分之一)。

在 ADC 板上、没有任何东西会生成该频率。 经过一些详细说明后、我们发现未使用的 JESD 通道上发生了一些具有恰好四分之一采样频率的事情。 由于 ADC 处于4通道模式、我假设未使用的通道应该断电、但它们要么未通电、要么正在进行其他操作。

提前感谢您的建议。