Other Parts Discussed in Thread: ADS54J64EVM, ADS54J64, ADS58J64EVM, LMK04828

主题中讨论的其他器件:ADS54J64EVM、 ADS54J64、 ADS58J64EVM、 LMK04828

我已开始修改 zc706_8b10b 参考设计、以便可以将 ADS54J64EVM 直接连接到 ZC706、但我遇到了一些问题。 我计划使用 ADS54J64是模式0 (LMFS = 4841)、并将采样率设置为280MSPS、这使得 ADC 的输出由于4倍抽取而达到70MSPS。

我的问题是:

ADS54J64EVM 上 ADS54J64的 sysref 和 CLKIN 引脚连接到 FMC 上的引脚、而 ZC706板上的引脚未连接。 这是否意味着在此设置中向 ADS54J64提供这些时钟的唯一方法是使用“ADS58J64EVM GUI”配置 EVM 板上的 LMK04828以提供280MHz 采样时钟? 每次打开电路板时是否都需要执行此操作? 由于 ADS54J64EVM Manual.pdf 未对此进行解释、是否有能够在 GUI 中设置正确设置的说明。

2、这和问题3相结合。 我对 MGT REF CLK 应该是什么有点迷失。 这应该是采样频率还是 ADC 输出速率? 这是否应该来自 LMK04828 (FPGA_JESD_CLK 或 FPGA_JESD_Sysref)、具体取决于您对问题1的回答? 该内核的用户指南仅说明“这些必须连接到 FPGA 的 MGTREFCLK 引脚”。 来自 ADS54J64EVM 上 LM04828的 FPGA_JESD_CLK 信号通过 FMC 连接到 FPGA 的 MGTREFCLK0引脚。 这意味着什么?

3.我的线路速率确切应设置为什么。 我找到了这个公式,其中 M=转换器数量,S=每帧每个转换器的传输样本数量,N’= JESD204B 字大小,FC=帧时钟,L=通道数。

通道速率=(MxSxN'x10/8xFC)/L

对于我的应用程序,M=8m S=1,N'=16,L=4,我认为。 我认为我的帧时钟为70MHz、因为我要以280MSPS 采样、模式0具有4倍的抽取率。 是这样吗? 如果是、我的通道速率应为2.8GSPS

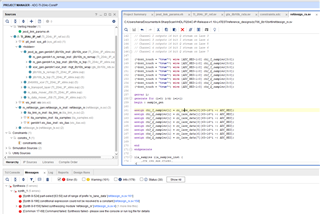

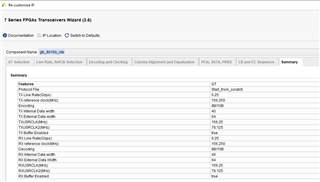

4.我已附加了修改后的 JESD_LINK_params.vh、GTX_8b10b_rxtx.SV 和 constrainations.xDC 文件以供参考。 我在 GTX_8b10b_rxtx 的“7系列 FPGA 收发器向导”中所做的唯一修改是,我在“线路速率,REFCLK 选择”选项卡中关闭了 TX。 我附加 了向导中的摘要图片以供参考。 通过这些修改、当我尝试合成时、我会得到 一个错误、我也将其作为图片附加。 我不知道为什么。 我最初将 refdesign_Rx.SV 文件中的 NUM_RX_CHANGE 更改为4、因为这是 ADC 具有的输出通道数。 我将其改回8并重新运行综合、但得到相同的错误。 根据 ADS54J64数据表、每个通道的 IQ 数据位于同一通道上。 我的目的是修改参考设计和整个封装、将其作为 IP、以便在更大的项目中使用。 我是否需要尝试封装整个参考设计?