主题中讨论的其他器件:ADS124S08、

大家好、

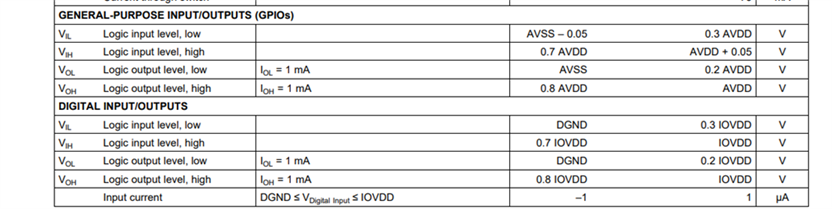

我们使用 ADS114S08和 ADS124S08来驱动 MOS、在数据表中、写入"当 IOL = 1mA 时、VOL 最大值达到0.2*AVDD"。 但是、现在我们的 MOS 栅极泄漏电流只有10uA、Vth= 0.3~ 0.7V、我们想知道 此时的最大体积是多少。 当 GPIO 为低电平时、我们必须要求 MOS 关断。 请帮助检查是否可行。

我期待您的回复!

此致、Hao

EC、FAE

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们使用 ADS114S08和 ADS124S08来驱动 MOS、在数据表中、写入"当 IOL = 1mA 时、VOL 最大值达到0.2*AVDD"。 但是、现在我们的 MOS 栅极泄漏电流只有10uA、Vth= 0.3~ 0.7V、我们想知道 此时的最大体积是多少。 当 GPIO 为低电平时、我们必须要求 MOS 关断。 请帮助检查是否可行。

我期待您的回复!

此致、Hao

EC、FAE

大家好、

抱歉、我需要详细描述问题如下:

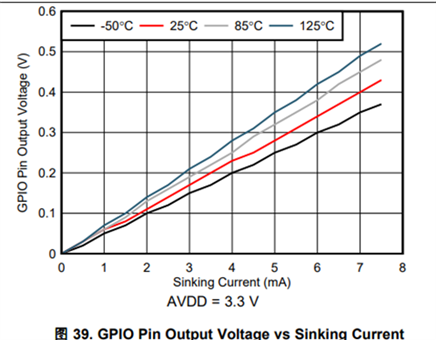

我们可以在 ADS124S08和 ADS114S08中看到图39、灌电流1mA 意味着 GPIO 输出电压低于0.1V、但 在电气特性中、我们可以看到最大 GPIO 电压达到0.2*AVDD=0.2*3.3=0.66V、这意味着 IOL 大于8mA、如图39所示。

请参阅图39、GPIO 可以直接连接 MOS (Vth 0.3V)、但可以看到电气特性、我们无法直接与 Moos 连接。 那么、如何理解图39和 电气特性呢? 哪个值是正确的?

我期待您的回复!

此致、Hao

EC、FAE

您好 Hao、

表和图都是正确的、但在解释所显示内容时可能会有一些误解。 电气特性表显示了特定条件下的器件响应。 条件是在25°C 时负载为1mA、这些数字是该运行的保证规格。

图39显示了不同温度范围和不同电流负载下的典型 GPIO 电流。 添加图39是因为许多客户将 GPIO 连接到非专用逻辑器件的器件。 需要了解和了解模拟 GPIO 在高于1mA 的负载条件下的行为。

互补 MOS 器件(CMOS)有源推挽驱动器级、在逻辑高电平时、在 NMOS 器件关断的情况下、接通连接到 AVDD 电源的 PMOS 器件。 逻辑低电平将关闭 PMOS 器件、并将 NMOS 器件打开至 AVSS。 在任何情况下、MOS 器件都有一些固有电阻。 电流越高 MOS 电阻上的负载越大、这将降低逻辑高电压并增加逻辑低电压。

图39中显示了负载的结果、其中当消耗的电流很小时、逻辑低电平接近0 (在本例中、AVSS 连接到 AGND) 当负载较高时、输出电压会随着 NMOS 电阻上的压降也增加而增加。

标准 CMOS 器件输入只会产生很小的负载影响。 结果是逻辑高电平的电压远接近 AVDD、逻辑低电平接近 AVSS。

至于图形和表格之间的差异、请记住一个是典型的、另一个是保证的。 会有很多批次和器件之间的差异。 MOS 器件导通时、MOS 器件的电阻可能会有所不同。 MOS 电阻的影响将取决于电流负载。

此致、

Bob B

您好 Hao、

保证值符合数据表中指定的条件。 无需进一步保证在较小电流下的性能。 原因是通过基本电路分析。 将 GPIO 视为模拟开关、其电阻值与开关的 RON 值相关联。 当打开低侧开关时、有一条通向 AVSS 的路径(使用单极电源的 AGND)。 我们可以将3.3V AVDD 的最坏情况开关电阻计算为 VOL (最大值)除以1mA 电流与保证规格值。 ((3.3V * 0.2)/1mA)的结果等于660欧姆。

如果我们现在计算10uA、则可以看到10uA * 660欧姆的电压、等于6.6mV。 这更接近0V、并遵循图39中的图。

此致、

Bob B