我们已经在测试实验室环境中使用 TI 的 ADC12DJ5200RF 评估模块与采集板已有很长一段时间。 我们已经在高达10GHz 的各种频率下使用了它、具有不同的时钟源和截取。 我们主要使用 JMOD1、它在几 个非 showstopper 例外情况下工作正常。 一个是时钟/4伪差杂散(占主导地位时间的一半)、另一个是 初始固件加载阶段的断续。 我们在共享相同 HSDC-Pro 的同一台计算机上安装了另一个 TI 的6.4GHz ADC 程序、否则可能与固件加载问题有关、我不会发布此问题、而是发布时钟/4杂散。

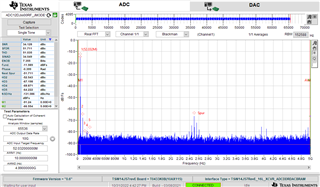

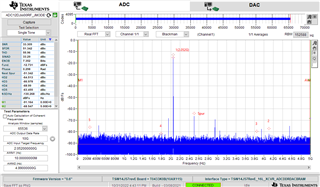

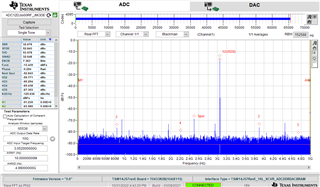

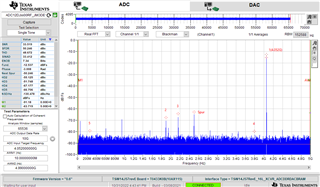

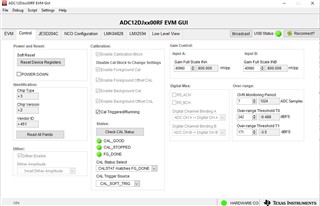

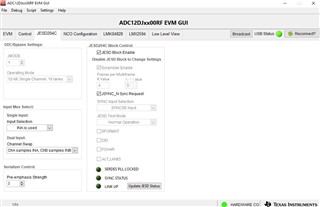

我们知道、我们在设置测量中看到的时钟/4杂散是由于与 ADC 交错和校准相关的因素或相关的因素所致、我们认为、很可能必须有一种方法来消除这种杂散。 我们已经尝试了可用的校准、使用了两个不同的板、等等。 有很多 JMODEE 和很多铃音和口哨,我并不是说要理解所有这些。 例如、不同的 JMODE 允许您使用不同的基准时钟和 ADC 模式。 我们 使用...进行了后台和前台校准。 还有其他特定于 ADC 的设置、还有其他特定于时钟截取的设置... 在继续评估时、我们仍在使用它、并在实验室中将其实际用于项目和一些与生产相关的测试。 让我感到很不高兴的是、我 无法消除我在这种配置中看到的这个时钟/4杂散。 在该设置中、我使用的是 JMOD1、DEVCLOCK=10GHz/2=5GHz、REFCLK=5GHz/20=250MHz、输入频率从直流到奈奎斯特、尝试后台 和前台校准等 随附了一些设置示例捕获以及 HSDC-Pro UI 捕获。

是否有人做过 类似的事情并遇到我们正在看到的10GHz/2=2.5GHz 杂散? 感觉像是校准\ADC 交错相关的东西... 还是不幸运、两个电路板的硬件都不好? 或者我们 是否完全缺少 重要的东西?

此致、

Mesfin。