Other Parts Discussed in Thread: DAC7728

Hallo、

我需要有关 DAC7728的一些帮助。

我需要在隔离环境中(通过光耦合器)模拟不同的电压电平。 电源也是无电势的。 我尝试按照以下步骤对 DAC 进行编程:

- R/W、CS、CLR、LDAC 和 RST 为高电平

-首先我设置地址位(A0至 A4)

-然后我设置数据值(D0至 D11)

-然后我将 CS 和 R/W 设置为低电平

--此时,我希望输出电压为 Vout0,但输出电压保持低电平

我还尝试在上电时将 LDAC 设置为低电平、但它不起作用。

随附的 pdf 中包含了原理图。 所有数据端口都具有与 D0相同的设置、为了获得更好的概述、它只被添加到原理图中一次(地址引脚也是如此)。

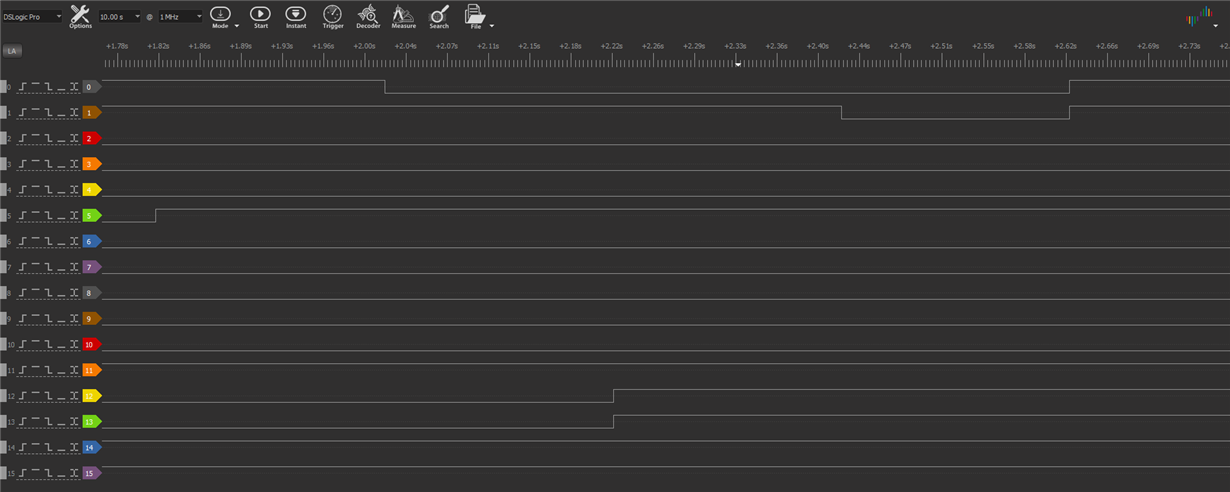

我使用逻辑分析仪检查了时序行为、这对我来说是可以的。

是否有一个基本示例可用于正确设置 DAC7728? 或者、我能否获得所附电路原理图的提示、其中存在什么错误/缺失?

提前感谢您。

Mario