请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE5808A 主题中讨论的其他器件: TSW1400EVM

戴尔

我需要有关 AFE5808A 问题的帮助。

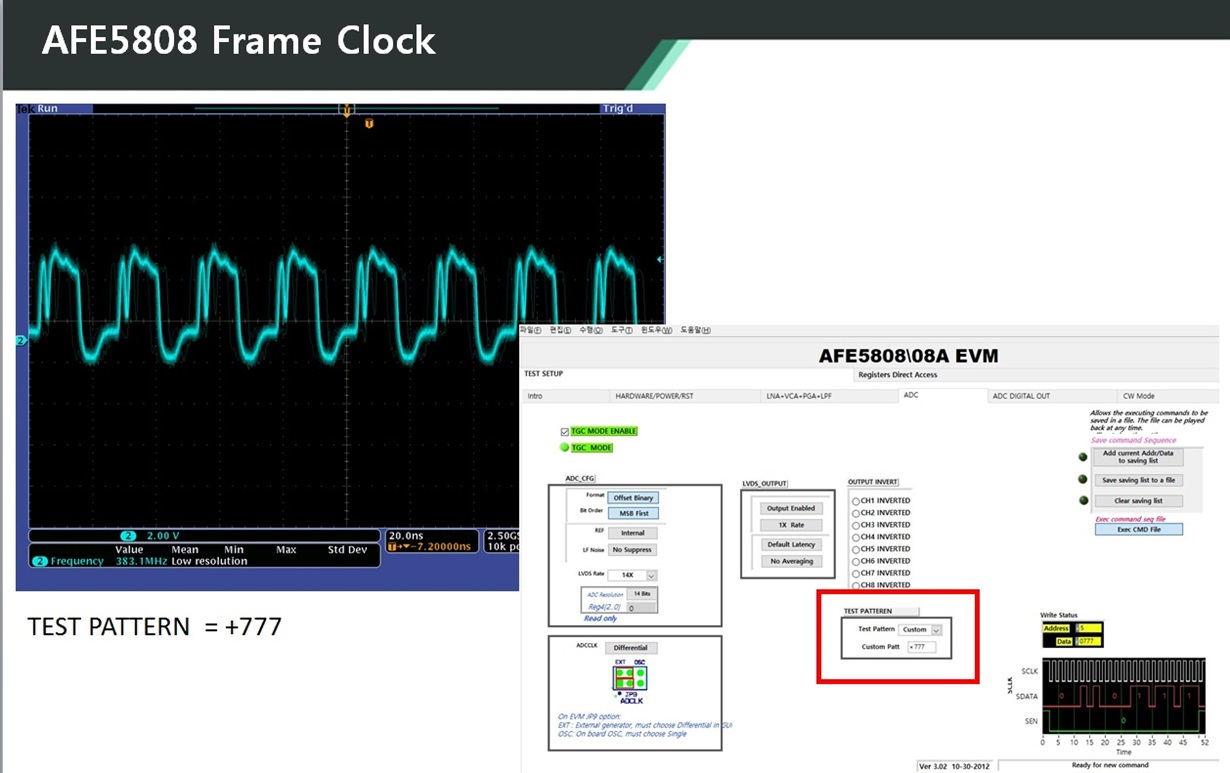

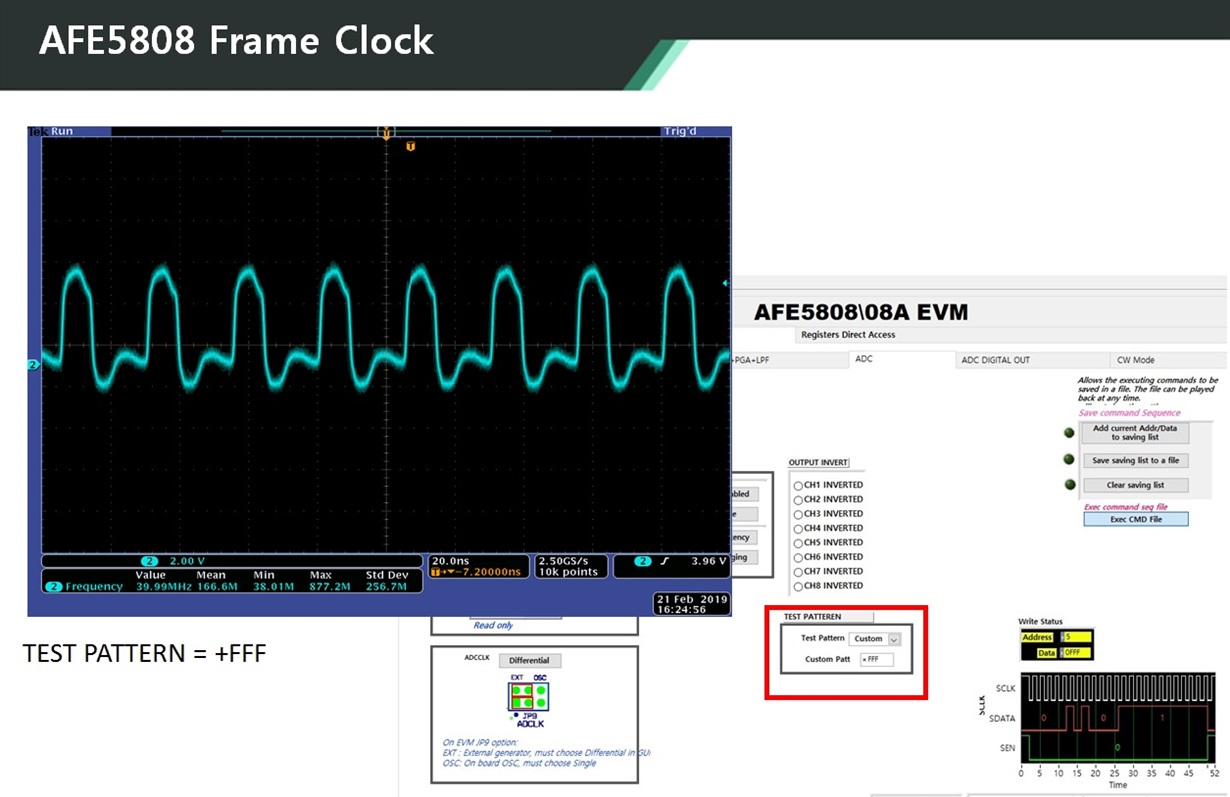

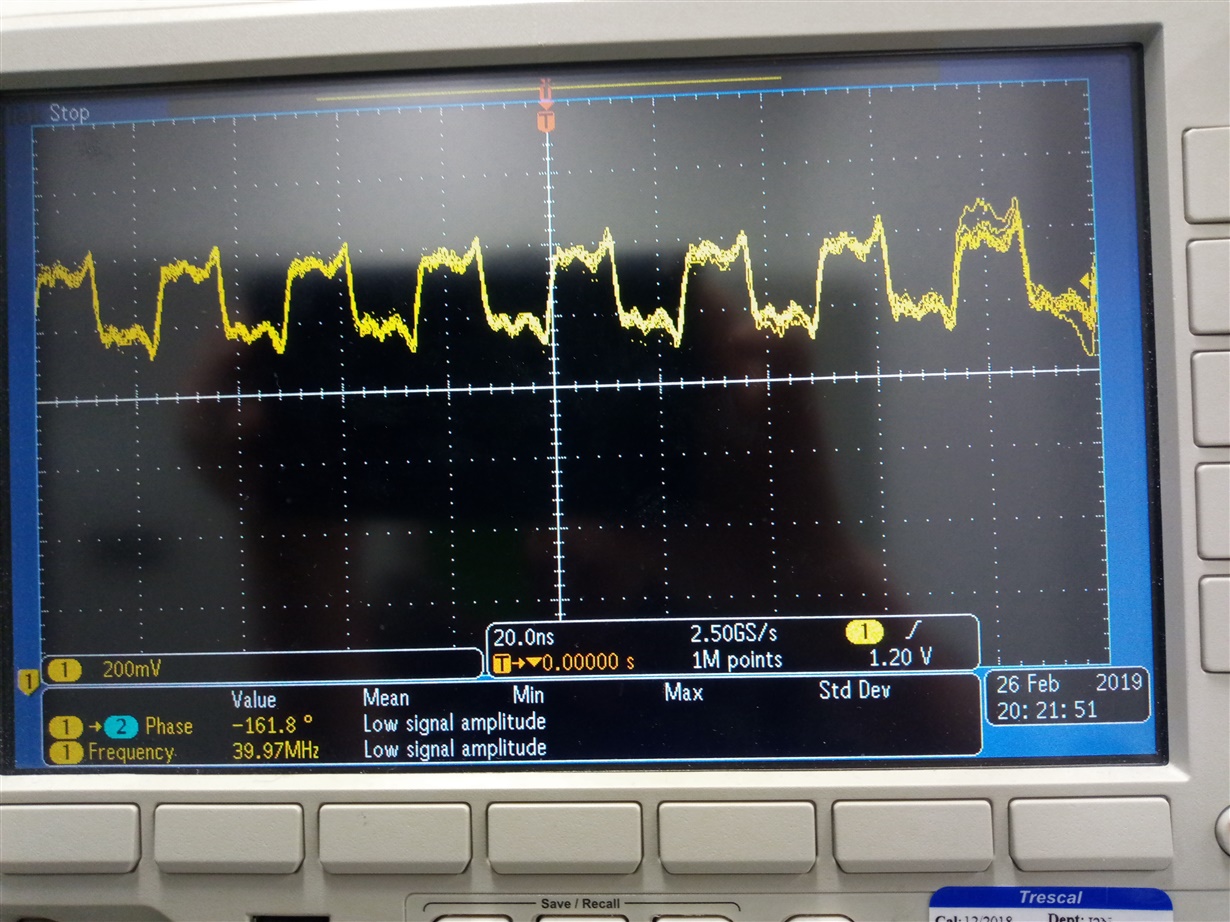

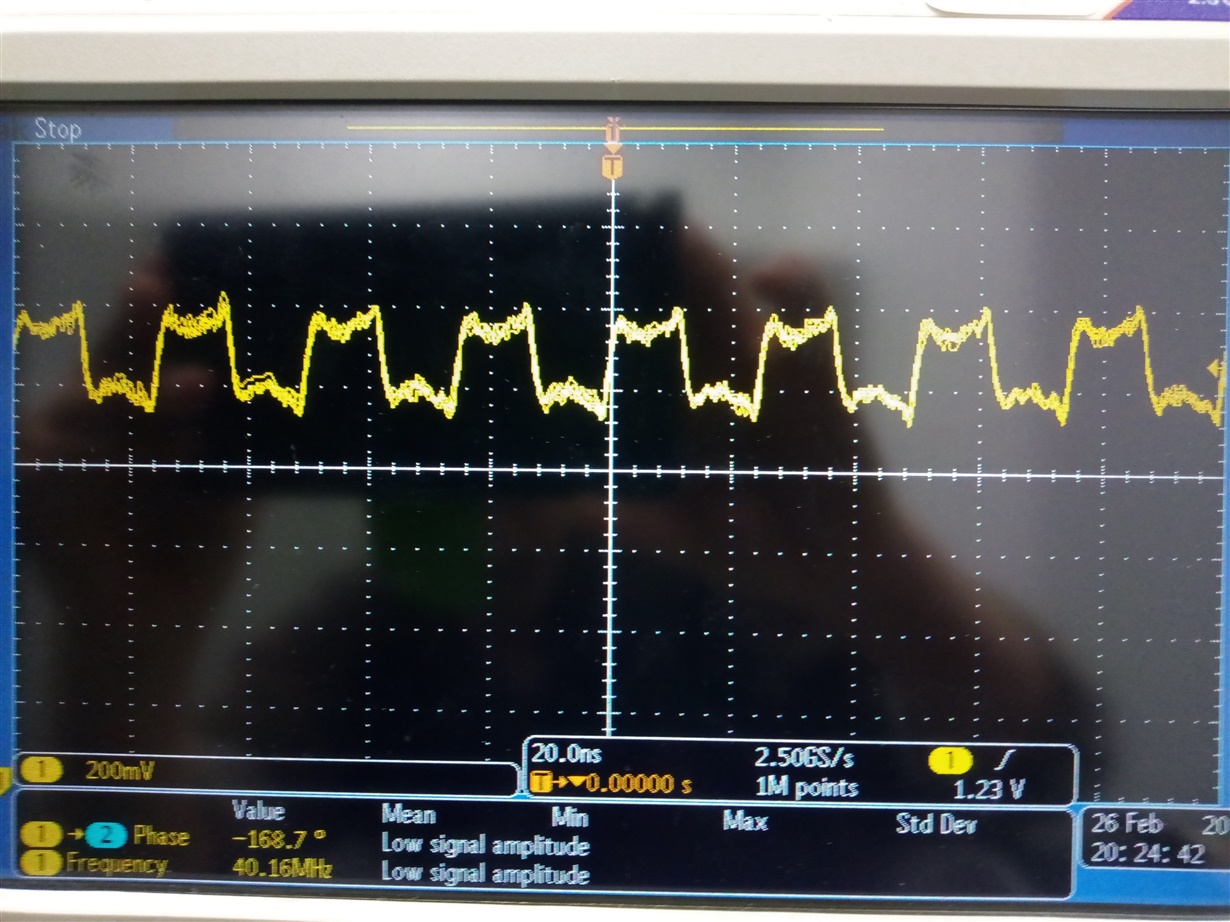

当 AFE5808A 的帧_CLK 输入到 FPGA (Cyclon 4)时、在 AFE5808A 的 UI 中输入"test PATTEREN"自定义数据会更改 AFE580A 的帧_CLK。

帧_CLK 是否会根据自定义数据输入的值发生变化?

谢谢你。