Other Parts Discussed in Thread: TLV2553, ADS8339

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV2553 主题中讨论的其他器件: ADS8339

您好!

我使用的是 TLV2553多通道 ADC。 输出引脚(数据输出和 EOC)连接到模拟器件电平转换器 P/N:ADG3304

出于某种原因、输出引脚不会一直降至零。

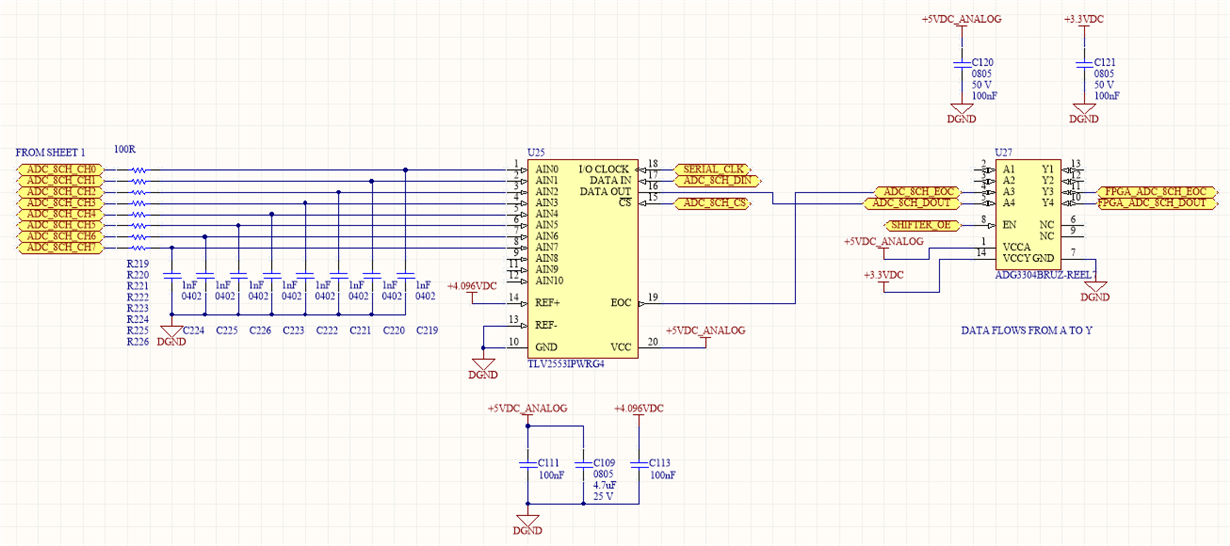

原理图如下:

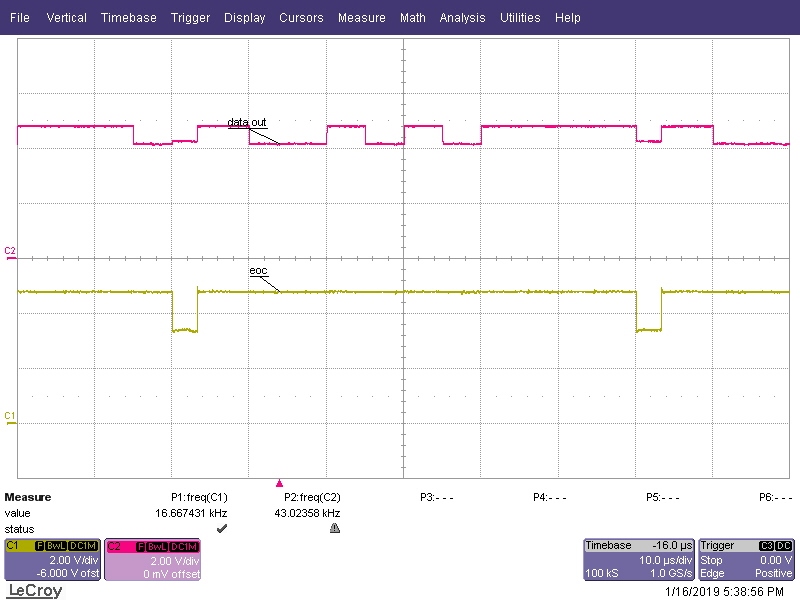

这里是输出引脚的波形。 "数据输出"在 U25引脚16处测量。 在 U25引脚19处测量"平机会"。

为什么这些信号在关断时间内不会下降到零伏?

请注意、我还将另一个器件 ADS8339的输出引脚连接到了同一电平转换器(单独的器件)、输出引脚降为零即可。

提前感谢