主题中讨论的其他器件:LMK04828

您好、Jim、

我有四个由 LMK04828和 FPGA (ZCU102)计时的 DAC38J84、尝试在所有四个 DAC 之间建立 JESD204B 链路。

LMFS = 2441

线路速率= 9.8304Gbps

使用单次 Sysref (通过 LMK 上的 SYNC 请求引脚触发)时的采样频率= 245.76MHz。

奇怪的是、我能够在我的四个 DAC 中的两个上建立一个链路并进行传输。 所有 DAC 具有相同的配置、而 LMK04828具有相同的寄存器值、用于进入每个 DAC 的时钟。

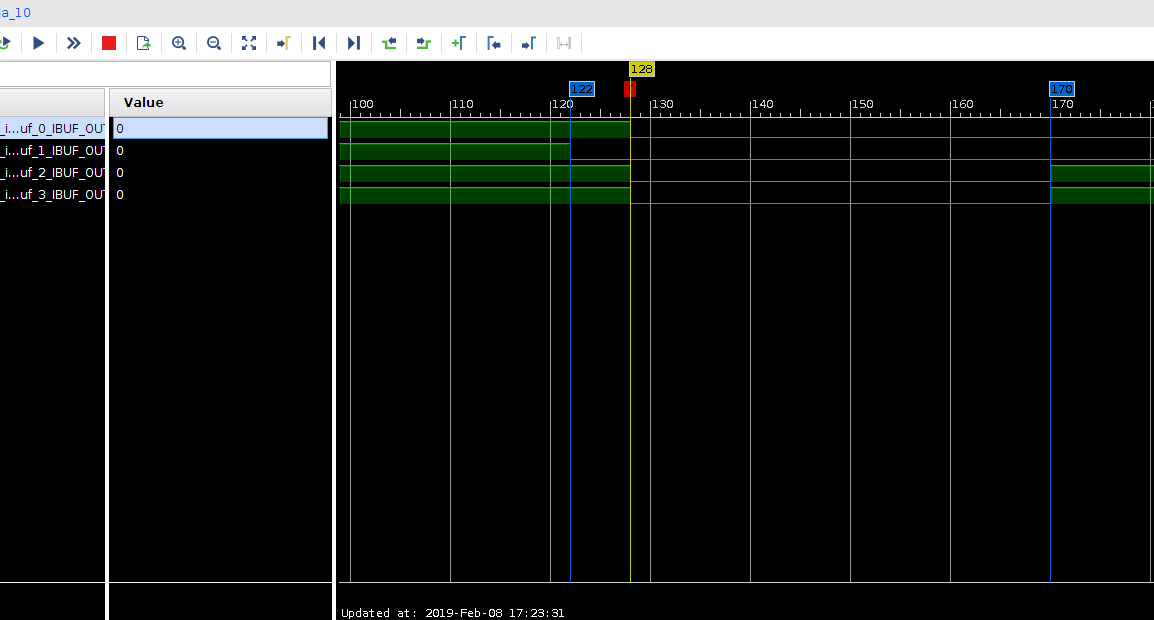

对于两个未建立链路的 DAC、在清除和读取以下寄存器后、我将在两个活动通道上获得 FIFO 警报:

通道2 (0x66)= 0x3或0xb 或0x703

通道4 (0x67)= 0x3或0xb

我知道这意味着 SERDES FIFO 读取或写入错误、但我们应该更改哪种类型来解决这些错误? 我们不认为我们的配置是相同的、因为它们都是相同的。 我在下面附上了它们。 我们有两个单独的文件、因为我们使用自己的工具对 DAC 和 LMK 进行编程(并且我们已经验证了 SPI 读取和写入工作正常)。