主题中讨论的其他器件: DAC5682Z、 LMK04828、 CDCM7005、 LMK04803、 LMK04133、 LMK03806、 CDCM6208

你(们)好

我正在从事一个大学项目、开发一个包含 ADC16dv160和 DAC5682Z 的电路板、两者都连接到 FPGA。

我需要时钟配置方面的帮助。

如果可能的话、我不想使用时钟发生器、而是直接从 FPGA (LVDS 信号)驱动它。 另一个简单的。

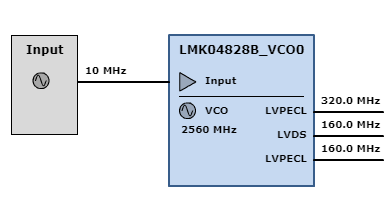

因此、DAC 需要320MHz 的 CLK 信号(PECL)和160MHz 的 DCLK 信号(LVDS)。 ADC 需要160MHz (可能是320MHz、我不确定)的 CLK_IN 信号(LVPECL)。

我可以通过某种方式将其组合在一起吗? 不是因为我的连接非常有限。 由于数据的大量、我只有2个通过 FMC 的时钟差分对。

我已经仔细研究了数据表、但我感到很困惑。 希望您能帮我完成设计。

我应该使用相同的160MHz 信号并在 LVDS 和 LVPECL 之间进行转换、还是可以对二者使用相同的信号? (数据表显示不建议将 LVDS 时钟用于 ADC)

是否有一个简单的时钟发生器只需要320MHz 的输入频率、然后输出上述频率和信号类型?

此致

Michelle