主题中讨论的其他器件:ADS1278、 ADS1178、 REF5025

您好!

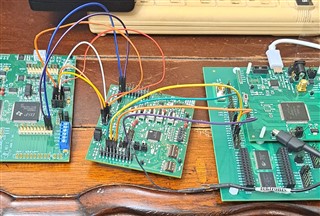

我通过 SPI 从 Cortex-M4处理器连接到 ADS1278 EVM。 我使用 MMB0为 ADS1278EVM 提供电源、CLK 和基准电压。 在为 MMB0 EVM 加电之前、我想确认这种方法。

突出显示的文本是一个问题、或者我正在寻求同意。 两者都位于表的最右列或以“•”表示的文本中

ADS1278EVM 已从 ADS1278EVM-PDK 物理移除

- MMB0用作为 ADS1278EVM 供电的电源

- 使用 S2开关设置模式、格式和 CLKDIV 线路、使用 S1开关为所有8个 ADC 通道供电、使用27MHz 的默认 S3开关设置 为 ADS1278计时

下面是我在上面所描述的内容。 下面是连接的详细信息。

|

S1. |

全部打开(上) |

为所有8个 ADC 通道供电 |

|

|

S2 |

(SPI、TDM、动态) F0、F1、F2全部“关闭” (模式[10]) M0“OFF”M1“ON” CLKDIV [0]“关闭” |

模式、格式和 CLKDIV 线路 |

|

|

S3 |

INT (右) |

使用板载振荡器为 ADS1278EVM 计时 |

缓冲器件 |

|

S6 |

串行接口格式 |

FS -帧同步格式。 [1-2]、[4-5]、[7-8]、[10-11] SPI - SPI 兼容模式。 [2-3]、[5-6]、[8-9]、[11-12] |

我跳转到了 SPI 兼容模式、 |

|

JP1 |

短整型 |

FSX 连接到 SYNC/DRDY |

我短路了吗? |

|

JP2 |

打开 |

FSR 未连接至 SYNC/DRDY |

我打开了它吗? UG 状态只能选择一个 |

关键独立连接:

|

功能 |

EVM 接头/引脚 |

MMB0 接头/引脚 |

Cortex-M4 接头/引脚 |

引脚名称 |

说明 |

|

|

|

SCLK |

J4.3 |

|

SPI2_SCK |

CLKX |

SCLK |

|

接口 |

DIN |

J4.11 |

|

SPI2_MOSI |

DX |

数据输入 |

|

|

DOUT |

J4.13 |

|

SPI2_MISO |

博士 |

数据输出 |

|

|

DRDY (SPI) |

J4.15 |

|

PORTF [10] |

内部 |

DRDY/FSYNC |

|

|

1.8V |

J5.7 |

J5.7 |

|

+1.8VD |

数字电源 |

|

电源 |

3.3V |

J5.9 |

J5.9 |

|

+3.3VD |

数字电源 |

|

|

5.0V |

J5.3 |

J5.3 |

|

+5VA |

模拟电源 |

|

模拟输入 |

通道1-4 |

J3.1-8. |

|

|

|

模拟输入 |

|

|

通道5-8 |

J1.3-10. |

|

|

|

模拟输入(ADS1178和 仅限 ADS1278) |

|

接地 |

||||||

|

|

DGND |

J5.5 |

J5.5 |

|

DGND |

数字地 |

|

接地 |

AGND |

J5.6 |

J5.6 |

|

AGND |

模拟接地输入 |

|

|

DGND |

J4.4. |

|

TP2 GND |

|

这是将 Cortex-M4 TP2 GND 连接到的正确板/引脚吗? |

|

基准电压 |

||||||

|

基准电压 |

REFN |

J3.18. |

J7.18 |

|

|

模拟输入 |

|

基准电压 |

REFP |

J3-20. |

J7.20 |

|

|

模拟输入 |

模拟输入

ADS1278EVM 的模拟输入连接到 J1和 J3。 将根据传感器数据表将四个器件连接到通道 J3 1-4。 S4、S5、S7和 S8默认为非缓冲信号。

基准电压

开关 S3从缓冲 REF5025中选择基准电压、并连接到基准引脚:

J3.18 = REFN 和 J3.20 = REFP -由 MMB0主板供电

|

模式[1:0] |

模式选择 |

CLKDIV |

最大 fCLK |

闪存模块 |

最大模块 |

OSR |

fCLK/Fdata |

最大 Fdata |

|

10. |

低功耗 |

0 |

13.5MHz |

fCLK/1. |

13.5MHz |

64 |

256 |

52.734kSPS |

这是否起作用?

安全吗?

我没有想到什么?

谢谢、

William