主题中讨论的其他器件: ADS54J60EVM、 ADS54J60、 ADS54J69、 LMK04828、 TSW14J57EVM

您好、TI 专家、

我的客户现在测试了 ADS54J69EVM、这里有一个问题。

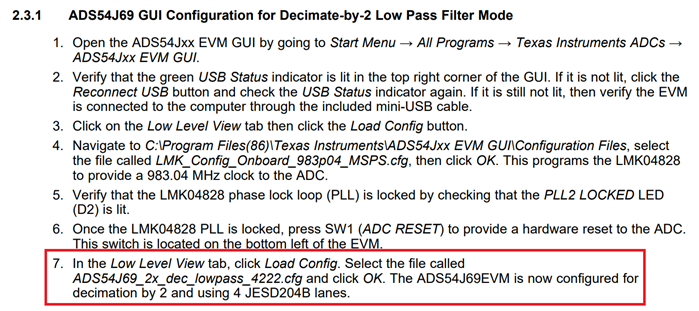

他们尝试在用户指南中评估2.3.1.7,但 在任何文件夹中都找不到“ADS654J69_2X_dec 低通_4222.cfg”。

您能否检查此配置文件的位置? 或者、请将此文件与您的帖子附上。

此致、

Chase

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 专家、

我的客户现在测试了 ADS54J69EVM、这里有一个问题。

他们尝试在用户指南中评估2.3.1.7,但 在任何文件夹中都找不到“ADS654J69_2X_dec 低通_4222.cfg”。

您能否检查此配置文件的位置? 或者、请将此文件与您的帖子附上。

此致、

Chase

你好 Chase、

我在实验室中没有手头上的 ADS54J69EVM、因此我使用 ADS54J60EVM 对此进行了测试。 我能够按照"用于2倍抽取低通滤波器模式的 ADS54J69 GUI 配置"过程捕获本底噪声、并加载"ADS54J60_2x_dec_lowpass_4222.cfg"文件并在 HSDC Pro 中选择"ADS54J69_2x_4222"。

如果您遇到问题、请尝试此操作并告知我们。

此致、Amy

Chase、

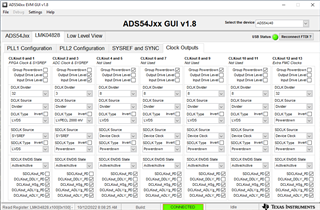

您能否让客户从 GUI 中为我们提供 LMK04828时钟选项卡? 客户是否希望 LMK04828提供250MHz 的输出来为 ADC 计时? Amy 发布的配置文件也适用于 ADS54J69、没有任何问题、只需修改时钟即可。 发布4个 LMK04828选项卡(PLL1配置、PLL2配置、SYSREF 和 SYNC、时钟输出)将帮助我们更快地对其进行调试。

此致、Chase

Chase、

附加了缺失的配置文件。

此致、

Jim

e2e.ti.com/.../8203.ADS54J69_5F00_2x_5F00_dec_5F00_lowpass_5F00_4222.cfg

***尊敬的 Jim:

感谢您的支持。

您注意到我的客户测试了配置文件、但结果相同。 可以再检查一下吗?

***尊敬的 Chase W, Amy,

请查看屏幕截图、如果有任何更改、请注意我。

下面是更多问题;

1.加载测试的配置文件后是否应输入一些命令? 还是仅加载配置文件、所有设置都已完成测试?

2、如何使用示波器检查 U4 (P1和 P2 -> FPGA_JESD_CLKP/M 和 P62以及 P63 -> CLK_LAO_0P/M)上的时钟信号?

我们需要在这2个引脚(P/M)之间连接任何电阻器、还是只需将探针的 GND 与任何引脚接触?

此致、

Chase

Chase、

完成第2.3.1节中的步骤7后、ADC EVM 上的 LED D2是否亮起? 如果此 LED 亮起、则在 HSDC Pro GUI 上单击"Capture"后、您要将 ADC EVM 连接到的 TSW14J56EVM 或 TSW14J57EVM 上的8个状态 LED 的状态是什么?

单击"Send"按钮后发送 HSDC Pro GUI 的屏幕截图。

此致、

Jim

尊敬的 Jim s:

感谢您的支持。

我的客户不使用 TSW14J56EVM 或 TSW14J57EVM、而是希望使用 FPGA 和自己的技术制作采集板。

因此、我们需要知道、请检查 ADS54J69EVM 是否在没有采集板的情况下正常工作。

1、我们如何知道此 EVM 是否正常工作? 如何检查 LMK04828的时钟频率?

我们最担心的是 LMK04828的250MHz 时钟频率。 我们如何检查该时钟?

2.我们想知道如何在 EVM GUI 中开始测试。 有任何开始按钮或其他图标。

请检查这2个问题。 谢谢。

此致、

Chase

Chase。

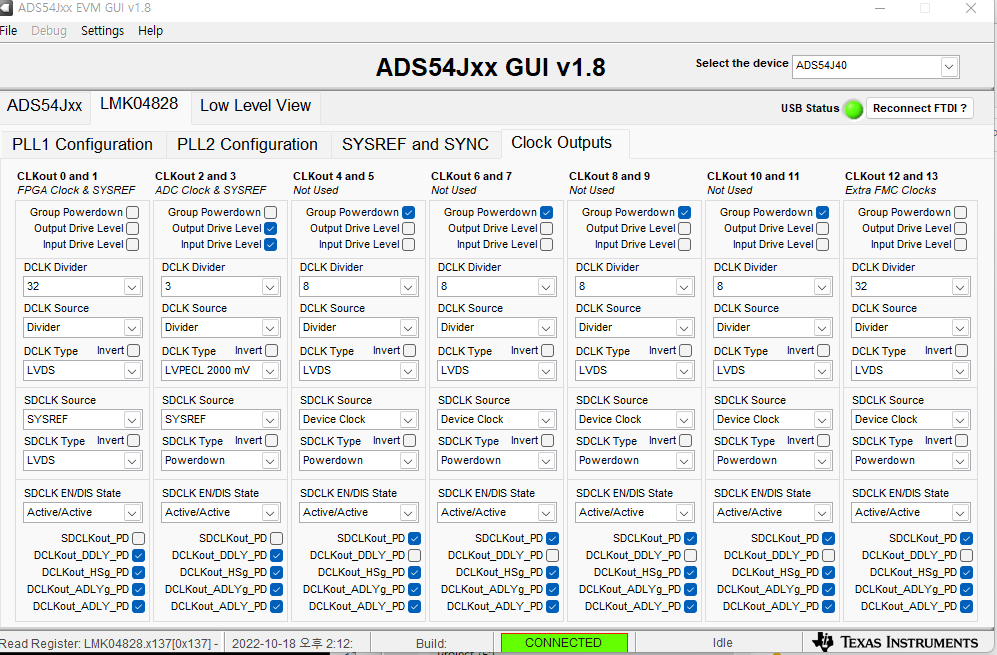

加载用户指南中提到的 LMK 配置文件后、确保 LED D2 (PLL2_LOCKED)亮起。 如果未打开、则说明您的设置有问题。

在 D2"打开"的情况下、转到下面显示的 GUI 中的 LMK0428时钟输出选项卡、并将 CLKout 0和1的 DCLK 分频器以及 CLKout 12和13设置为"32"。 对于 CLKout 12和13、取消选中"Group Powerdown"、因为默认情况下配置文件会关闭此输出。

您的设置应如下所示。 现在、您应该在位于 EVM 底部靠近 LMK04828 (U4)的电容器 C93、C97、C79和 C80上看到92.16MHz 时钟。 该频率是 PLL2 (2949.12MHz)除以32的 VCO 频率。

此致、

Jim

尊敬的 Jim s / Chase W:

感谢您的支持。

我的客户对 LMK04828的时钟输出做了一些测试、但看不到所需的时钟。

请参阅下面的设置屏幕截图;

他们刚刚使用设置检查了92.18MHz 时钟信号。

正如我所说、他们将使用 Xilinx FPGA (UltraScale+ AUP25)、因此他们需要与 JESD204B IP 兼容的时钟。 (100MHz、125MHz、156.25MHz、250MHz 等)

我认为 JESD204B IP 有一些参考设置。 您能否检查其初始设置? (尤其是 PLL1、PLL2和时钟输出选项卡)

此致、

Chase

Chase、

使用 EVM 上组装的当前 VCXO (122.88MHz)、它们只能生成此频率的倍数的时钟频率(122.88MHz、245.76MHz、368.64MHz 等)。 对于所需的频率、它们必须为电路板提供外部时钟或更改 VCXO 器件。 如果他们将此部件更改为100MHz VCXO、他们将能够创建100MHz、125MHz、156.25、250MHz 等。

如果它们为 SMA J6提供一个2500MHz 外部时钟、则可以在时钟分配模式下使用 LMK04828生成这些频率。

让我知道客户更喜欢使用哪种选项、我将为此方法发送 LMK 设置。

此致、

Jim

Chase、

当 VCXO 为100MHz 时、附加的 LMK 配置文件将为 ADC 创建1GHz 时钟、为进入 FPGA 的两个时钟创建100MHz 时钟。

此致、

Jim

e2e.ti.com/.../LMK_5F00_Config_5F00_Onboard_5F00_1000_5F00_MSPS_5F00_FPGA_5F00_100M.cfg