主题中讨论的其他器件: CDCLVD1216、 AFE5832LP、 AFE5816

您好!

我们有一个包含多个 AFE5851器件的设计。 它们接收相同的20MHz 采样时钟、并在10MHz 帧时钟上生成它们。

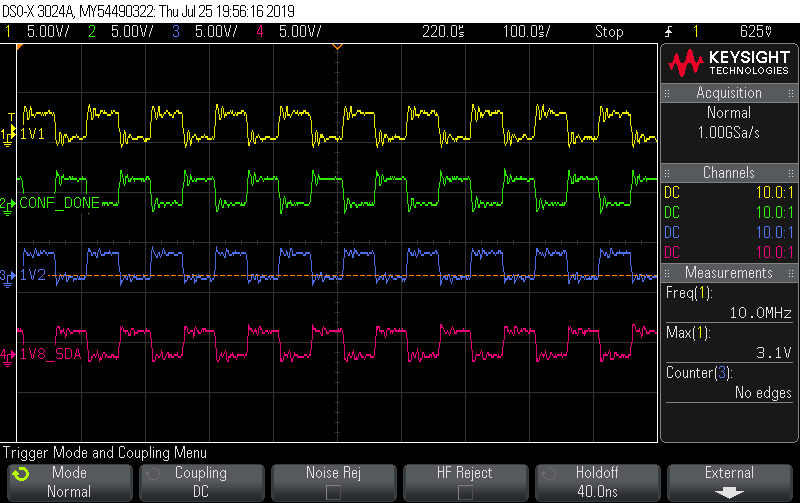

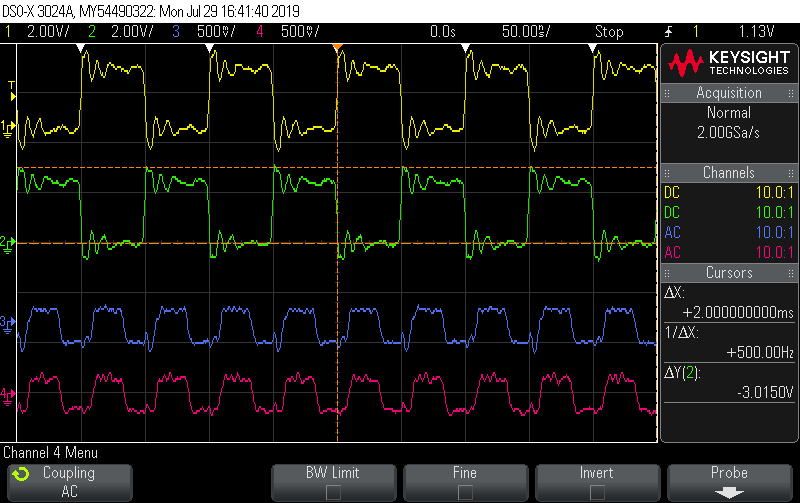

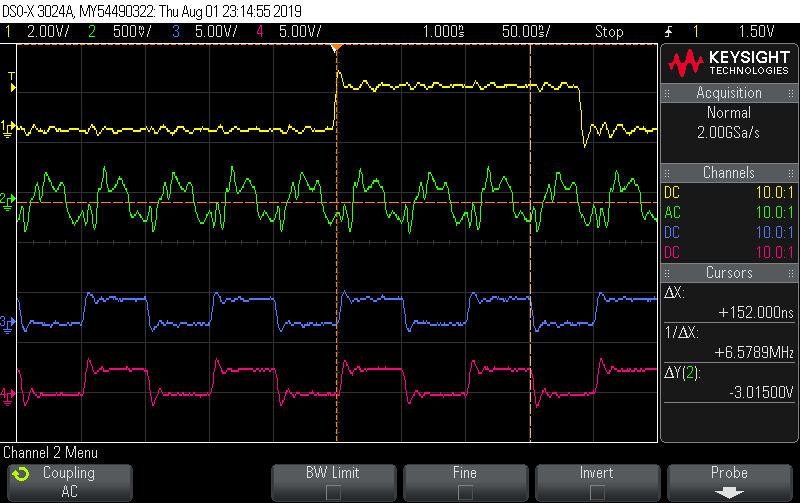

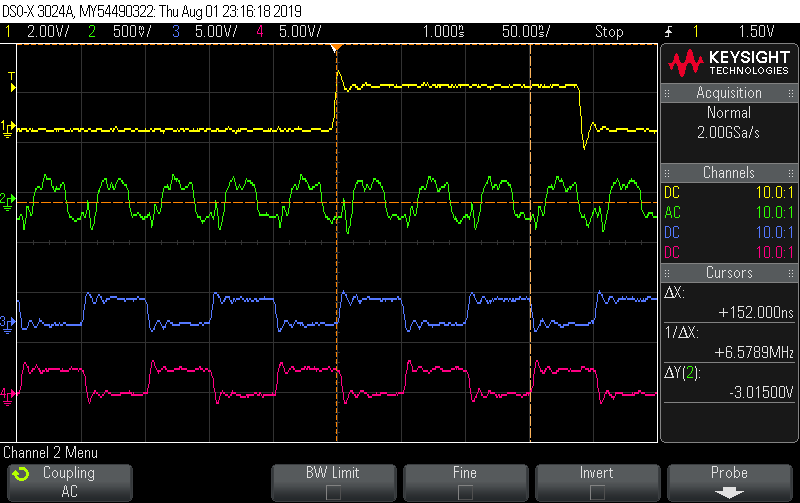

但是、我们观察到帧时钟不是同相的。 请参阅下图(忽略标签)、其中显示了4个不同 AFE5851的帧时钟。

由于我认为帧时钟与实际采样时刻密切相关、因此上述两个 ADC 在50ns 后采样、而另外两个 ADC 采样。

是否有任何方法可以将它们相互同步? 我尝试使用中央控制的 PDN 信号来实现这一点、但这并不成功。 最大的

问题是、加电后、不同的 AD 转换器与之前的转换器是同步的、这在这些器件之间增加了随机50ns 的变化。

感谢你的帮助。

此致、

Peter