主题中讨论的其他器件: CC1101

尊敬的专家:

是否有人可以解释以下内容?

在数据表(例如、第10页)中、有一个与上述内容相关的文本:"FSAMPLE = 200ksps 至500ksps、FSCLK = 3.2至8MHz、FIN = 40.2kHz"。

在同一数据表中、我们可以找到被写入的文本、即 ADC 在 SCLK 的3D 周期后开始转换。

如果 ADC 时钟比 SCLK 低16倍(最后一个数字可根据数据计算)、ADC 如何能够转换输入信号?

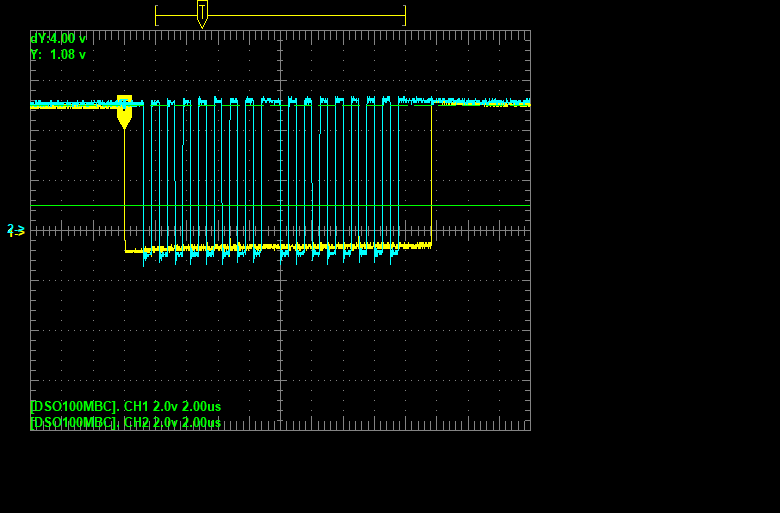

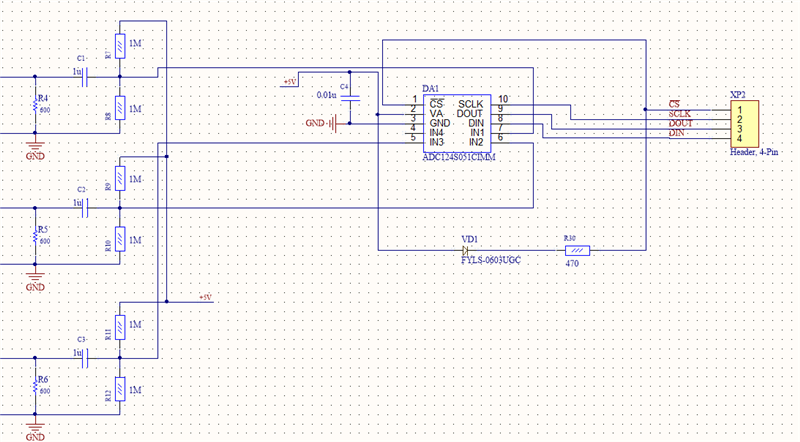

我尝试 在 某种电压表中使用 ADC124S051。 如果我测量直流电压、我会得到很好的结果。 如果我尝试测量交流电压、结果非常不准确。

谢谢!