尊敬的先生

我开发了一款具有 TI ADC12D1800RFIUT、FPGA 和 ZBT Cypress SRAM 的电路板。

在硬件中、每个 ADC/SRAM 由一个单独的 LDO 供电。

FPGA VCCC/AUX 内核电压由直流/直流稳压器供电。

遇到的问题

--------

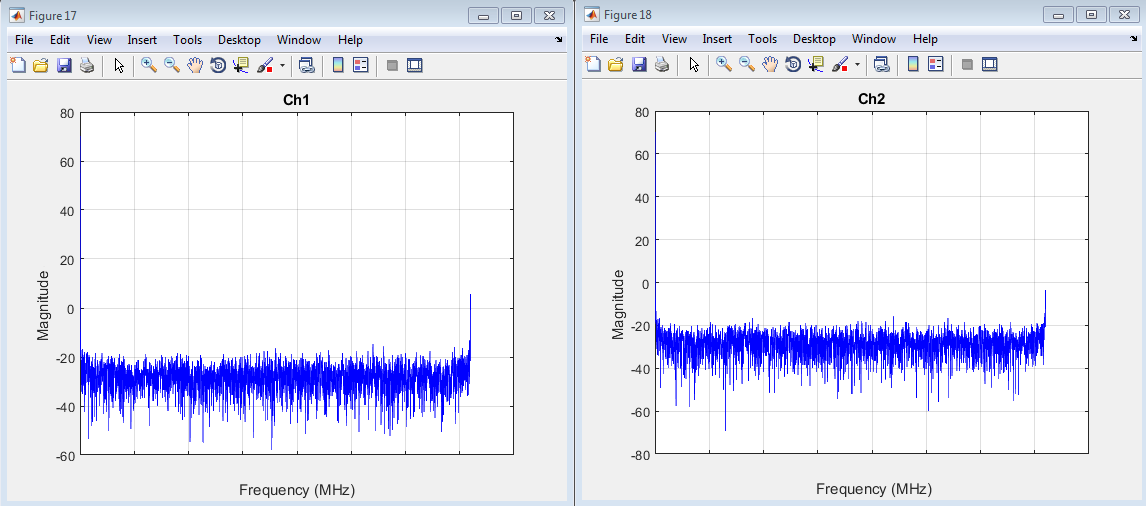

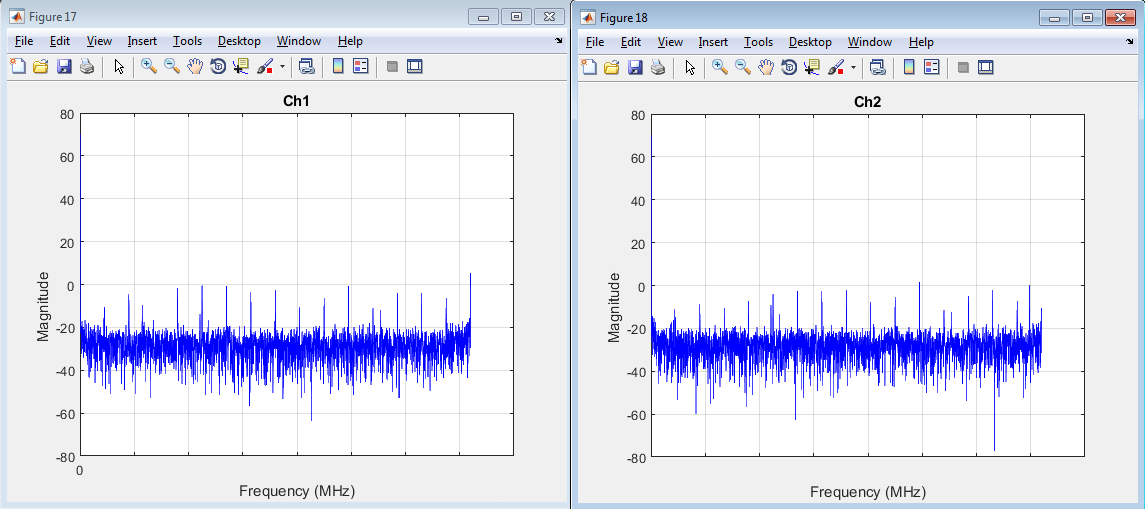

1) 当 FPGA 执行 SRAM 读取操作时、我遇到了 ADC 杂散。

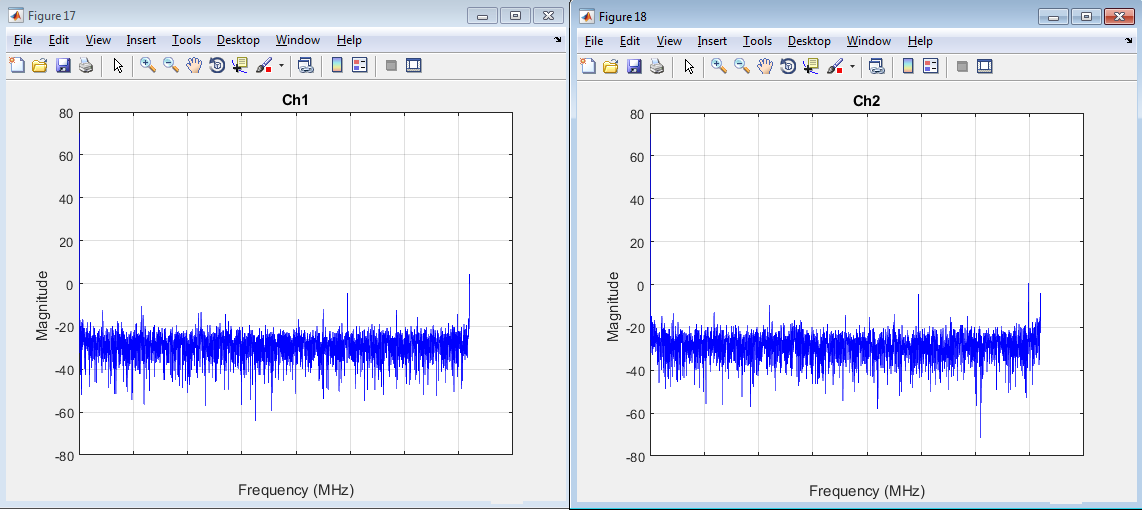

2) 当 FPGA 执行写 SRAM 操作时、不会出现太多伪波。

3) 当 FPGA 不执行任何读取/写入 SRAM 操作时、ADC 性能良好。

我做了什么

--------

a.)我曾尝试降低 SRAM 时钟、杂散将仅跟随谐波。 我还尝试将数据切换率从100%降低到25%、杂散会在整个频谱范围内传播。

ADC 频谱以供您参考。 ADC 模拟输入端接至50欧姆。

我还尝试了以下方法

b)激活 ADC 测试模式在执行 SRAM 读取操作时、ADC 测试模式被验证为正确。 这意味着 SRAM 和 ADC 之间没有任何数字串扰干扰。

我已经阅读了数据表、TI 建议 AGND/DGND 不需要任何隔离、并且可以连接在一起。

是否有人对上述问题有任何解决方案/建议?

希望尽快收到您的回复

此致、

Alex

在 SRAM 处于空闲状态时捕获 ADC 数据(无 SRAM 读取/写入)

连续读取 SRAM 时捕获 ADC 数据

连续写入 SRAM 时捕获 ADC 数据