主题中讨论的其他器件: REF5050

尊敬的 Sirs:

我正在测试新电路板的第一个样片、其中、除其他外、还有一个 DAC8728原理图附在下面。 使用所有必需的时序正确管理 DAC 总线。 没有问题。 我的疑问来自引脚 RSTSEL (和 USB#/BTC)的管理、这些引脚来自锁存器(HCT273)的输出、因此在上电时处于低电平。 此外、所有其他输入信号都来自相同的锁存输出(CLR#、RS#、LDAC#)。

我们的软件人员更倾向于将 RSTSEL 和 USB#/BTC 设置为逻辑1、以供其使用 DAC。 因此、他执行以下操作:

1) 1)保持 RST#为低电平

2) 2)将 RSTSEL 和 USB#/BTC 设置为高电平

3) 3)将 CLR#设置为高电平

4) 4)将 RTS#设置为高电平

DAC8728在双极-10/+10V 范围和二进制补码值下工作正常。

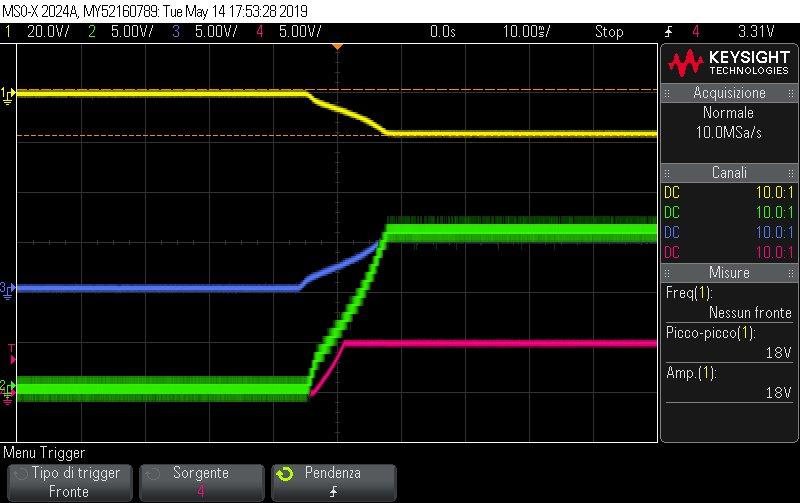

然后、在工作几个小时后、如果我们关闭 PC 并(甚至立即)上电、DAC 行为会发生变化(s/w 当然是相同的)、并且 RST#信号设置为高电平后、DAC 行为立即发生变化、 我们看到所有输出立即变为+10Vdc、DAC "似乎"认为在0至30V 的范围内为单极。 当然、正弦 AVDD 为+15V、无法达到30V (或20V)。 问题是我们无法再正确驱动它、这种行为很危险、因为模拟运动驱动器会使电机以最大速度启动、从而损坏机器。

即使我们多次关闭系统并重新为其供电、DAC 也会保持这种奇怪的行为。

如果我们用冷冻喷雾剂喷洒 DAC、然后再次通电、DAC8728将返回正确的行为。

原理图的设计如您所见(我是说锁存器273的数字控制输入)、可为软件设计人员提供灵活性、但我的疑问是、如果 DAC8728在上电时对数字输入进行"采样"、 那么、这种管理看起来是错误的、因为(当然) RSTSEL (和 USB#/BTC)在上电时确实被采样为低电平(因为 HCT273输出在上电时被复位为低电平)。

奇怪的是(数据表中未记录)、当 DAC 处于冷态时、在上电后对 RSTSEL 和 USB#/BTC 进行的更改似乎效果完美。 这似乎只是在工作了几个小时后才出现问题, 只有在我们断电后再加电时才会出现问题。

我的问题是:

- 我是否坚持 RSTSEL 和 USB#/BTC 直接连接到 IOVDD 而不是来自 HCT273输出?

(因此、在上电时、根据需要对其进行高电平采样) - 当 HCT273输出被 s/w 设置为高电平时、您能否尝试解释为什么这些信号在加电后正确设置 DAC8728?

它们是否应该在上电时已经"采样低电平"? - 冷/热启动时不同行为之间的关系是什么?

因为我们需要 100%安全、在 RST#被移除(变为高电平)后、DAC8728会在启动时将所有输出设置为零。

提前非常感谢您的支持。

此致

此处连接:DAC8728电路。